编者按

在不久之前,半导体行业观察发布了题为的文章对芯片技术的未来进行了探讨。在本文里,我们将深入探讨一下3nm以后的晶体管支撑技术。

多层排线技术支撑3纳米

在之前的文章中,我们探索了“更先进的晶体管技术(Post Silicon)”,具体而言,通过将作为2D材料的过渡金属二硫属化物(TMD,Transition Metal Dichalcogenide)用于沟道(Channel),以实现1纳米以下技术节点的目标。

本文开始介绍第五项“新一代多层排线技术(BEOL)”。负责3纳米以后技术节点的多层排线技术(BEOL)是本文的主题。首先,我们看下微缩化技术蓝图。

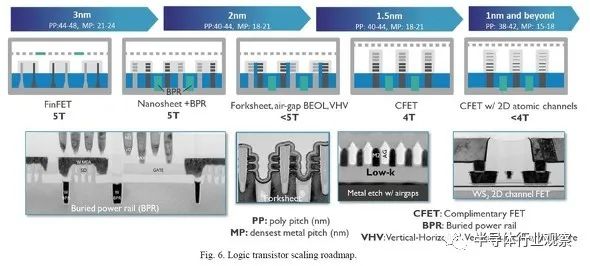

3纳米以后的CMOS逻辑电路的技术蓝图

排线微缩化技术蓝图。此图是笔者根据上面图纸中排线的相关数值汇总的

三年来,金属排线的最小Pitch(MP)的技术发展蓝图如下:5纳米技术节点为28纳米、3纳米技术节点为21纳米、2纳米技术节点为16纳米。此外。CGP的发展蓝图如下:5纳米技术节点为48纳米、3纳米技术节点为45纳米、2纳米技术节点为42纳米。

而从最新的技术蓝图中可以看出来,金属排线的微缩化发展越来越慢。3纳米节点的MP为21纳米一一24纳米、CGP(或者PP)为44纳米一一48纳米。2纳米节点和1.5纳米节点的MP为18纳米一一21纳米,CGP为40纳米一一44纳米,1.0纳米以下节点的MP为15纳米一一18纳米,CGP为38纳米一一42纳米。在以往的技术蓝图中,金属排线的Pitch(MP)微缩化是从21纳米直接过渡到16纳米。而在最新的技术蓝图中,21纳米的后面为18纳米、15纳米,发展较缓。

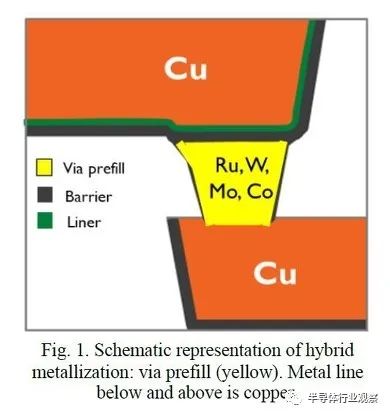

支持着最新的CMOS逻辑电路的多层排线技术采用的是铜(Cu)质排线。而制造工艺采用的是Damascene技术(一种通过蚀刻绝缘膜,在沟槽中镀金属的技术,俗称“大马士革技术”或“镶嵌技术”)和CMP技术(一种平坦化技术)。

铜(Cu)质排线的缺点是随着微缩化的发展,排线的电阻会急剧增加。由于铜原子易于扩散于周边,因此将Barrier层(防止铜原子扩散)置于铜金属层与绝缘膜之间。而Barrier层电阻高、很难做到更薄。因此,如果缩小铜排线层断面厚度,Barrier层(高电阻层)的厚度就会增加。

要缓解因微缩化而带来的电阻增大问题,有两个办法。其一,加厚铜排线层。其二,将排线金属改为不需要Barrier层的材料。在imec演讲中,主要叙述了“尝试将排线金属由铜(Cu)改为钌(Ruthenium)”。

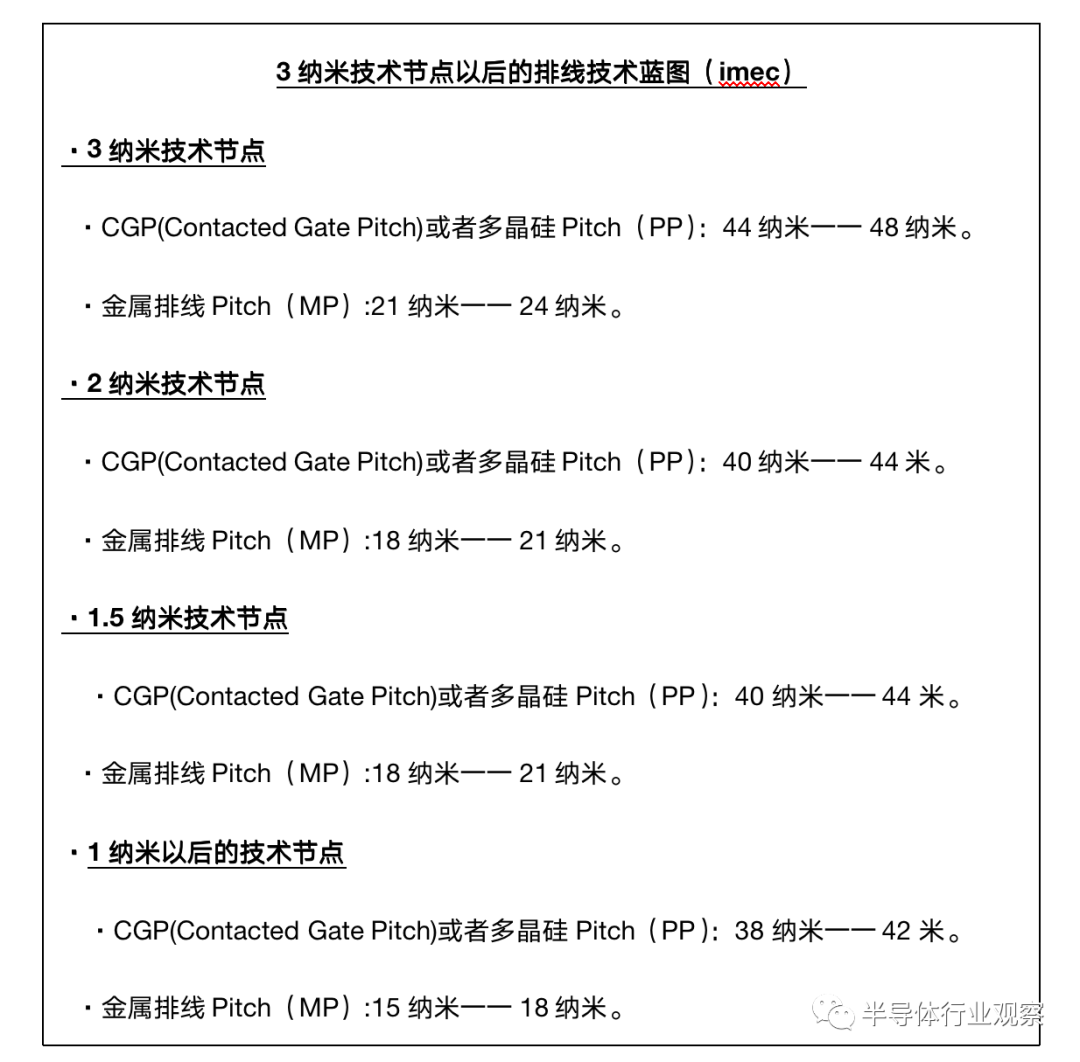

即使在现行的Lithography (微影)技术中,也做到与16纳米(2纳米技术节点)Pitch平行的平行线路。将ArF浸液光刻技术与Multi-patterning技术(多重图形技术)融合。Multi-patterning技术选用的是SAOP(Self Aligned Octuple Patterning,自对准型八重曝光)。依据以上这些技术,imec于2018年公布称,已经成功试做与16纳米Pitch平行的排线线路。

电子显微镜下观察,与16纳米Pitch平行的排线线路断面图

新的多层排线技术有助于实现2纳米

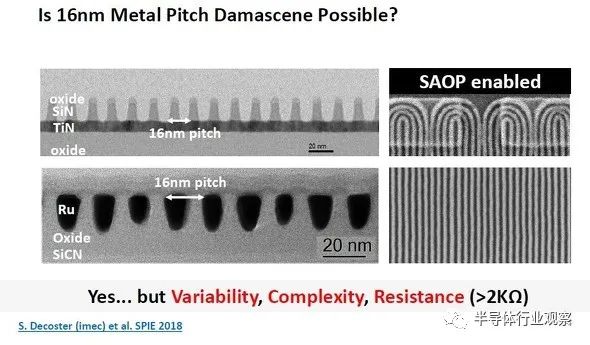

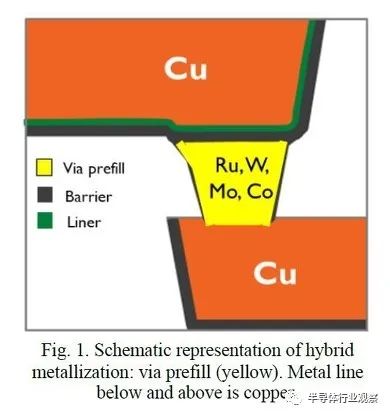

多层排线的导体部分由平行的直线排线群层(排线层)和连接各层的导孔(Via)电极构成。*迎来微缩化极限的是导孔电极。于是,导孔电极的材料不再采用铜,而是改为钨(W,Tungsten)、钼(Mo,Molybdenum)、钴(Co,Cobalt)、钌(Ru,Ruthenium)等熔点较高的金属。

多层排线断面图:排线层为铜、导孔电极为熔点较高的金属

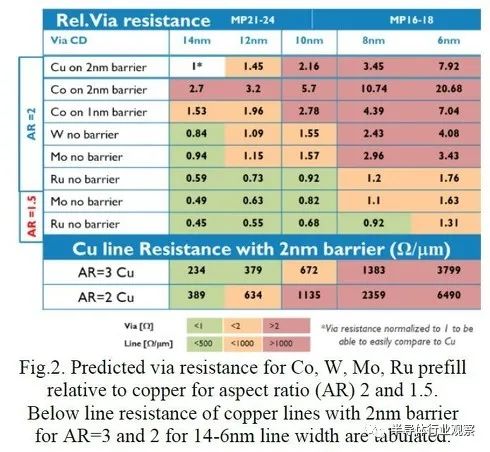

因导孔电极微缩化而引起的铜和高熔点金属电阻值的变化(比较铜和其他高熔点金属,上图中的数值为计算值)。用铜填埋纵横比(Aspect Ratio,AR,Barrier层厚度为2纳米)为2的导孔(最小尺寸CD为14纳米)时的电阻值定为单位“1”后,得出以上数值。

用厚度为2纳米的Barrier层和铜来填埋最小尺寸(Critical Dimension,CD)为14纳米的导孔(相当于排线Pitch为21纳米一一24纳米的多层排线结构)后,把导孔的电阻值(导孔的纵横比AR为“2”)定为单位“1”。如果导孔宽度微缩至10纳米,电阻值(相对值)会超过单位“1”的两倍以上,为2.16。

另一方面,同样导孔(AR为2)最小尺寸为14纳米,且无Barrier层的钨电阻值(相对值)为0.84,钼为0.94,钌为0.59,电阻值都低于铜。

此外,当排线宽度为14纳米、纵横比(AR)为3时,铜质排线的电阻值(此处为:每单位长度的电阻值)为234Ω/μm,AR为2时,铜电阻值为389Ω/μm。如果排线宽度微缩至10纳米,当AR为3时,电阻值为672Ω/μm,当AR为2时,铜电阻值为1135Ω/μm,电阻值增加到2.9倍。

基于以上推测,imec认为未来钌(Ru,Ruthenium)有望成为多层排线材料。其理由如下:电阻率低、不需要Barrier层、可进行蚀刻加工等。

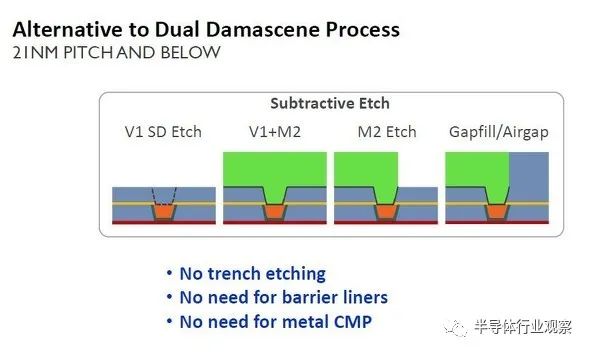

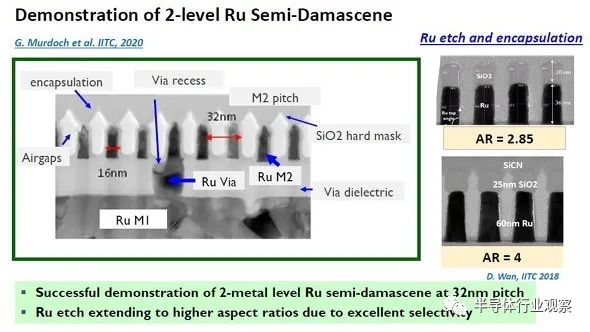

于是,imec正在利用一种被称为“半镶嵌(Semi Damascene)”的技术,来研发钌材质的多层排线结构。在“半镶嵌”技术中,首先在下层的排线层上形成绝缘膜,并蚀刻形成导孔。其次,同时在上层的排线层(Ru层)和导孔上形成绝缘膜。最后,蚀刻导孔周围后,用绝缘膜填埋、或者留下“空气间隙(Air Gap)”。

“半镶嵌(Semi Damascene)”技术工艺。利用成膜和蚀刻,形成排线和导孔电极。导孔的周围为绝缘膜或者空气间隙

从铜排线改为钌后的技术蓝图

Imec正在利用一种名为“半镶嵌(Semi Damascene)”的技术研发钌(Ru,Ruthenium)多层排线结构。就“半镶嵌(Semi Damascene)”的技术而言,它是在下层排线层的上面形成绝缘膜、蚀刻导孔。然后,在上层的排线层(Ru层)和导孔上形成绝缘膜。最后,蚀刻导孔周边后,用绝缘膜填埋、或者留下“空气间隙(Air Gap)”。

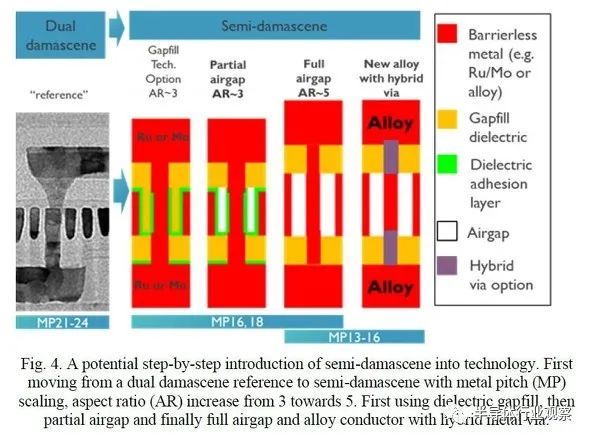

从铜排线改为钌(Ru,Ruthenium)排线后的微缩化技术蓝图在“IEDM 2020”的演讲(论文编号 32.2)中已经公布。21纳米一一24纳米Pitch是采用“双镶嵌结构(Dual Damascene )”技术形成铜排线或者钌排线。钌排线和“半镶嵌技术”都是始于16纳米一一18纳米Pitch。相邻的排线之间和上下排线层之间由介电常数较低的的绝缘体填充。排线的纵横比(AR比:纵/横之比)为2.5左右。3也是被选项之一。

即使是16纳米一一18纳米Pitch,在进入下一代际后,也会将排线的纵横比(AR比)提高至3,降低电阻值。通过在相邻排线间的绝缘层中留出一部分“空气间隙(Air Gap)”,来控制静电电容值的增加。

在新的代际(16纳米一一18纳米Pitch之后的13纳米一一16纳米Pitch)中,会把排线的AR比提高至5,以进一步降低电阻值。相邻排线间的绝缘层全部由“空气间隙(Air Gap)”完成,以控制静电电容值的增加。

要实现13纳米一一16纳米Pitch,采用钌金属会存在不少困难。因此很有可能会采用其他金属或者合金用于排线、导孔电极。

从铜排线向钌排(Ru)线的过渡,钌排线微缩化发展蓝图

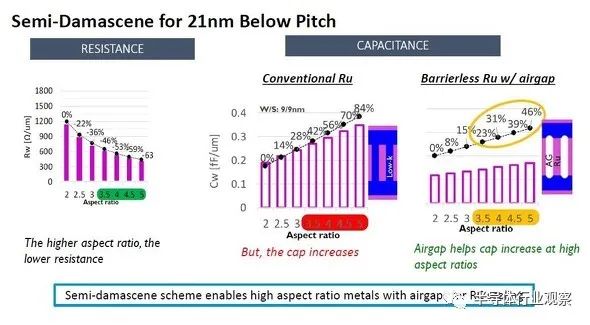

下面我们说明一下导入微缩化技术蓝图的技术要素。排线微缩化的主要弊端在于电阻值的增加和较低的抗电迁移(Electromigration)性。但是二者都可以通过提高排线的AR比得以缓解。比方说,将AR比从2提高至3.5的话,单位长度的电阻值可以下降50%左右。

但是,如果提高AR比,就会出现排线间静电电容值增加的问题。比方说,如果将AR比从2提高至3.5,单位长度的电容值会增加42%。

要解决这一问题,可以在相邻排线间的绝缘部分导入“空气间隙(Air Gap)”。“空气间隙(Air Gap)”的相对介电常数(Relative Permittivity)为“1”,理论上是介电常数*的绝缘物体。一旦导入“空气间隙(Air Gap)”,就可以将AR比为3时的静电电容值控制在23%。

钌(Ru)排线的AR比和电阻值以及静电电容值的关系。电阻值和静电电容值都基于单位长度的

Imec已经成功用钌(Ru)试做了32纳米Pitch(采用“半镶嵌”技术和空气间隙技术等)的两层排线。*层金属排线、导孔电极、第二层金属排线全部采用钌材质。

电子显微镜下观察,*层金属排线、导孔电极、第二层金属排线全部采用钌材质的双层排线结构的断面图,排线Pitch为32纳米

导孔电极的微缩化支撑高密度化

接下来,我们谈谈多层排线技术的核心一一导孔电极技术。

导孔电极指的是连接上下排线层的圆柱状的电极。由在排线层间的绝缘膜中形成的细长孔和埋于孔中的金属构成。通常,与排线层的厚度相比,导孔电极的直径较短。如果收窄排线的宽幅,导孔电极就会增加、抗电迁移(Electromigration)性也会下降。如果将铜质多层排线微缩化,铜导孔电极的电阻会明显增加,同时,电迁移(Electromigration)的寿命会变短。于是,考虑仅把导孔电极的金属改为熔点较高的金属。这在上文已经说明。

多层排线层的断面图,其中排线层为铜、导孔电极(黄色部分)为熔点较高的金属

最尖端的CMOS的多层排线多采用以下布局(Layout),各层平行的直线群通过上下相连的层来直接相连。比方说,从最下层(*层或者称之为“M1”)开始数,奇数层的排线为水平方向(横向)延伸,偶数层(第二层或者称之为“M2”),的排线为垂直方向(纵向)延伸。由于一般的导孔电极是连接上下相连的排线层的,因此此处的导孔电极为连接水平排线和垂直排线的交叉点。

但是,最近,人们开始认为连接邻近奇数层(或者偶数层)的导孔电极也很重要。比方说,用导孔电极连接M1和M3。这种导孔电极的作用是可以有效降低下层排线的电阻值,提高抗电迁移(Electromigration)性。

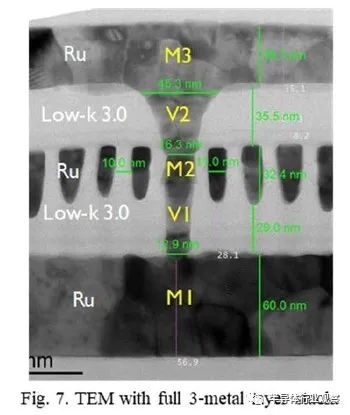

电子显微镜下观察,钌(Ru)材质的三层排线层的断面(试作品)。M2(第二层)为横切、M1(*层)、M3(第三层)为平行方向。M1何M3的排线Pitch为36纳米、M2为21纳米,导孔(Via)的直径(V1,连接M1和M2的导孔)为12.9纳米,V2(连接M2和M3的导孔)为16.3纳米一一45.3纳米

通常,三层排线的最上层和最下层由2个导孔电极和1层排线层连接。为了方便,我们将连接M1和M2的导孔成为“V1”,称连接M2和M3的导孔为“V2”。要连接平行的M1和M3,需要经由2个导孔和1个排线层。即,V1、M2、V2。M2是用于连接V1和V2的,因此不是具有细长的排线,因此多采用柱状。我们这种结构为“叠加导通孔(Stacked Via)”。

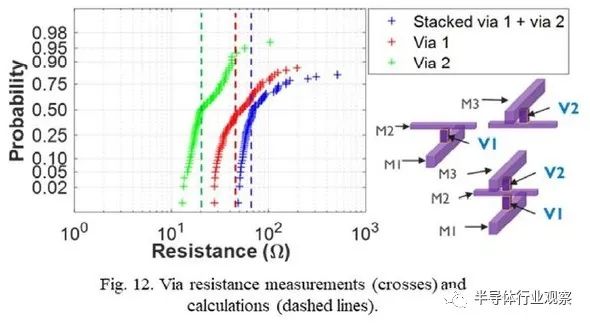

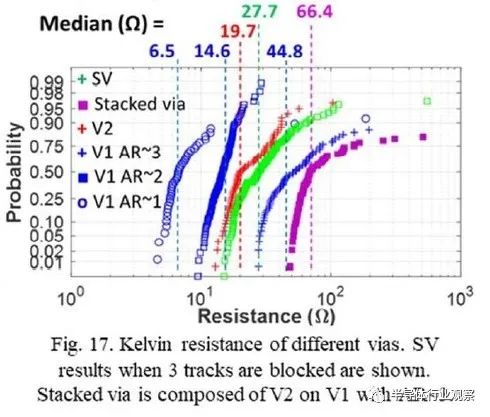

导孔电极的电阻值(累积概率)。此处为导孔电极的试作品的测量值

就imec试做的钌材质的三层排线而言,中间的M2的Pitch最狭窄,因此,V1的电阻稍高,V2的电阻稍低。此外,V1、M2、V2“叠加导通孔(Stacked Via)”电阻最高。

降低叠加导通孔(Stacked Via)电阻的方法之一是将M2层做得厚一些,但是,如果M2做得过厚,就会影响周边的M2的配置,影响整体的布局。此外,直接连接M1和M3(不经过M2)的“Super Via(超级导孔)”也在被人们考虑,将在下文中叙述。

“Super Via” 可有效降低多层排线的电阻

接下来我们就“Super Via(超级导孔)” 技术展开叙述,这是一种可以降低直接连接奇数层(或者偶数层)的导孔电极的电阻的技术。

现在已经开始采用一种名为“叠加导通孔(Stacked Via)”的技术,即一种以垂直方向连接奇数层(或者偶数层)的导孔电极。下面我们设想一下连接*层金属排线(M1)和第三层金属排线(M3)的导孔电极。利用“叠加导通孔(Stacked Via)”技术,首先制造出连接M1和第二层金属排线(M2)的导孔(V1),然后制作M2。其次,再制造连接M2和M3的导孔,最后成膜制成M3。

叠加导通孔(Stacked Via)技术的缺点如下,与连接M1和M2(或者M2和M3)的导通孔电阻相比,连接M1和M3的电阻值的电阻值会变得较高,且导孔的生产工艺会很复杂。

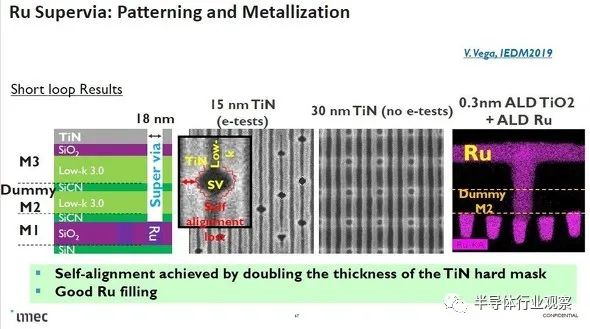

于是,开始考虑一种可以直接连接M3到M1的“Super Via(超级导孔)”。制作工艺如下:首先制作M1和M2(或者Dummy M2,即虚设的M2),然后在M2上形成绝缘膜。其次,堆叠氮化钛(TiN, Titanium Nitride)硬膜(Hard Mask),然后开凿一个可以贯通到M1表面的垂直孔(即,Super Via)。最后,将高熔点金属(比方说钌)埋入到超级导孔(Super Via)内,同时,形成M3。

连接第三层金属排线层(M3)和*层金属排线层(M1)的超级导孔工艺。左边为结构图,M2为虚设层(Dummy)。右边图像为在X射线扫描电镜能谱仪(EDS设备)和电子显微镜下观察的形成M3后的断面图。中间的两张图像如下,各种厚度TiN层所对应的导孔的类型。如果将TiN层做到30纳米,就可以获得良好的导孔

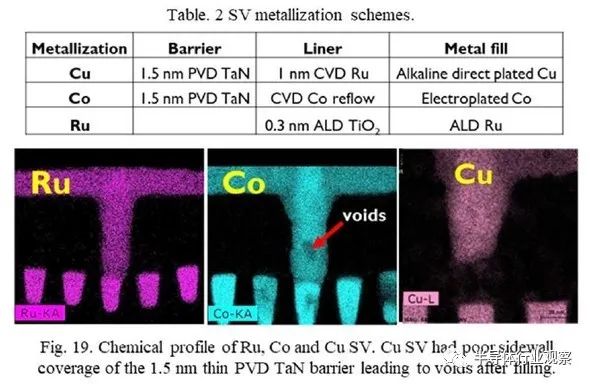

Imec分别试做了铜(Cu)、钴(Co)、钌(Ru)材质的可以连接M1和M3的超级导孔,结果如下:铜无法充分地填埋导孔底部内壁,钴会使导孔电极内部发生Void(空孔)。能形成良好的导孔电极和M3的只有钌。

上图是试做的铜(Cu)、钴(Co)、钌(Ru)材质的可以连接M1和M3的超级导孔。上面的表格是Barrier层、Liner、排线金属、成膜方法。下面的图片为在EDS设备和电子显微镜下观察的断面图像

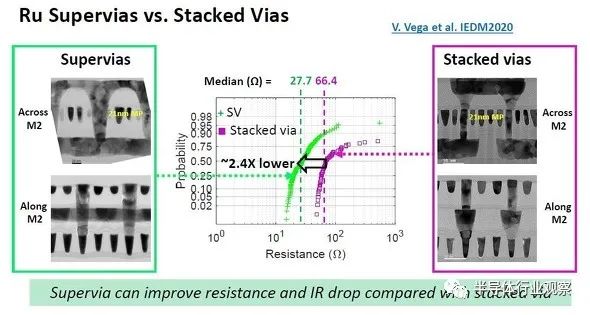

后来,又试做了钌材质多层排线,并比较了采用之前的技术叠加导通孔和超级导通孔情况下,连接M1和M3的导孔的电阻值。M1和M3为互相平行的直线群、排线Pitch为36纳米;M2为与M1(以及M3)成九十度的平行直线群,排线Pitch为21纳米。

利用传统技术试做的导孔电阻值(中间值)为66.4欧、超级导孔为27.7欧。超级导孔的电阻值较传统技术减少了1/2.4(42%),得以大幅度减少。

超级导孔(左边)、传统技术(Stacked Via,右边)下的电阻值(测定值)。图像为电子显微镜下观察的断面图。排线Pitch如下,M2为21纳米,M1和M3为36纳米

“Super Via”所面临的问题

Imec所推测的超级导孔有效发挥作用的排线结构如下:连接*层金属排线(M1)和第三层金属排线(M3)。理论上的标准单元如下:垂直方向(纵向)上为平行的直线状的M1和M3,水平方向(横向)上为平行的直线状的第二层金属排线层(M2)。在此标准单元下,如果想要直接连接M1和M3,M2肯定是一个“障碍物”。换句话说,是超级导孔技术“阻碍(Block)”了M2。

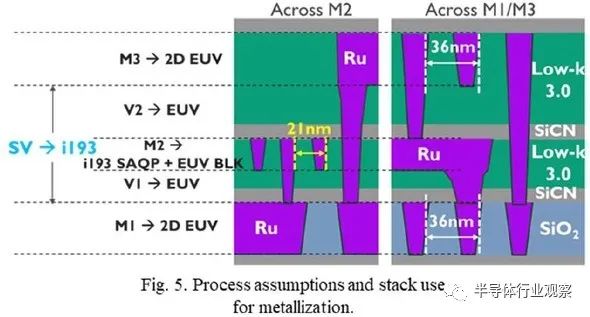

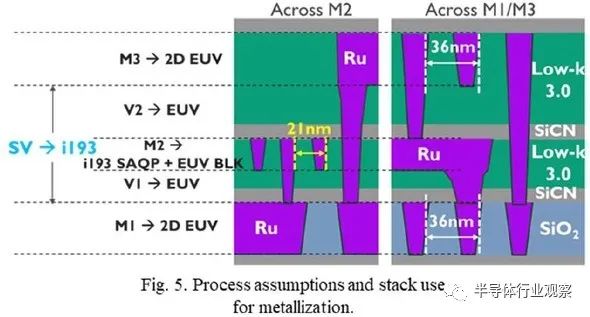

3纳米代际下,从*层(M1)到第三层的多层排线结构和光刻技(Lithography)。排线层和导孔电极的金属为钌。左图为第二层(M2)的断面图,右图为M1和M3的断面图

一个超级导孔可以阻断(Block)多少根(Track)M2?至少是1根。但是,imec使用的3纳米代际的多层排线的尺寸如下,M1和M3为36纳米Pitch,M2为21纳米Pitch。用超级导孔“阻挡(Block)”Pitch最短的M2。如果仅阻挡一根的话,对M2的布局没有什么影响,但很难再保持超级导孔和M2的绝缘关系。

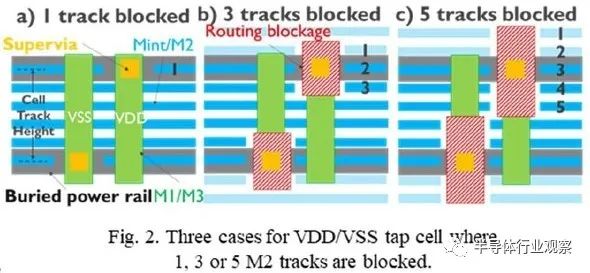

单元格(Cell)高度为5T(Track)的标砖单元(Standard Cell)中的超级导孔和第二层金属排线(M2)的布局。上图为超级导孔所“Block”的M2的多条线路。左(a)为1根,中间(b)为3根,右(c)为5根

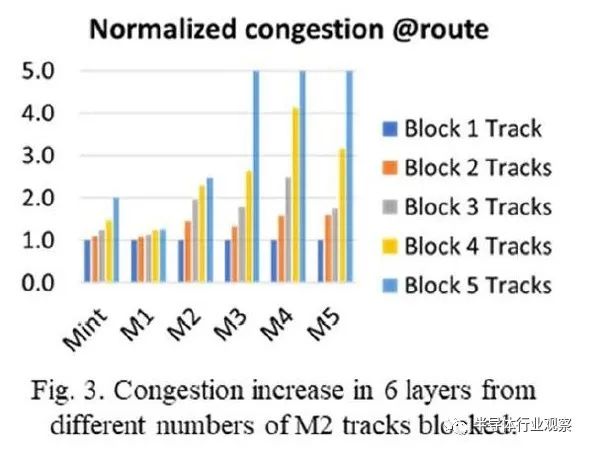

下面我们看看增加阻断(Block)的线路后的影响。如果被阻断(Block)的线路数量过多的话,M2的布局就会受到阻碍。其影响如下,当布局第三层以及网上的其他层时,会受限制,且排线会更复杂。Imec将阻断(Block)的M2的线路数量从1根(Track)到5(Track)分别作了测试,且推断了从第0层(Mint层)到第5层(M5)的排线复杂程度。我们把阻断(Block)一根排线的复杂程度为看做单位“1”,阻断3根(Track)的时候,复杂程度没有什么变化,4根和5根的时候,从M3到M5的复杂度急剧增加!

超级导孔所阻断的M2的线路数量与从M0(Mint)到M5的排线复杂度的关系。当阻断的线路数量超过3时,M3和M4、M5的排线复杂程度急剧增加。即,把阻断(Block)一根M2排线的复杂程度为看做单位“1”

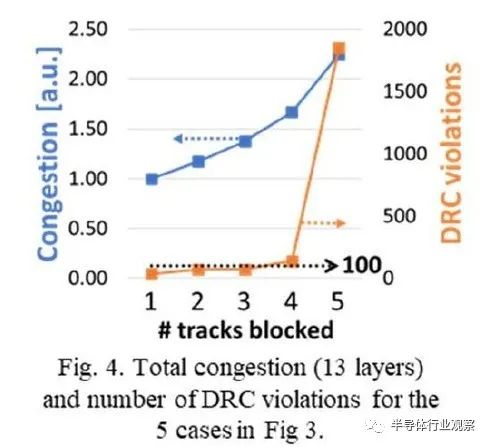

此外,如果阻断的线路条数过多的话,布局的设计就会很困难。多层排线的布局设计(PnR工程)工艺中使用设计工具能够检测出布局是否违反设计规定的功能(即,设计工具检查功能,DRC)。当超级导孔阻断的M2的线路数量增加的时候,排线的复杂度会增加,同时,违反DRC的数量也会增加。假设一款13层的排线结构,当阻断的M2的线路达到5条时,违反DRC的数量会达到1500,甚至更多。另一方面,当被阻断的数量小于4时,违反DRC的数量为100左右。

被阻断的M2的线路数量和排线复杂度(左纵轴)、违反DRC数量(右纵轴)的关系。当被阻断的线路数量为4以及以下时,违反DRC的数量为100左右。当数量为5时,违反DRC的数量会急剧增加,超过1500。以上为13层产品的推测值

接下来,我们将说明当减少单个超级导孔阻断的排线数量时产生的问题。布局在垂直(竖向)方向的*层金属排线层(M1)和第三层(M3),第二层金属排线层(M2)为水平(横向)方向的平行直线。并采用了Nano-sheet结构的晶体管和埋入式电源(BPR)。超级导孔直接连接M1和M3。即,超级导孔阻断了M2。

*层(M1)到第三层(M3)的多层排线结构、光时刻(Lithography)技术(3纳米代际)。排线层和导孔电极的金属为钌。左图为第二层(M2)的断面图。右图为M1和M3的断面图

为了尽可能地提高排线布局的自由度,需要减少阻断的排线数量。单个超级导孔至少要阻断一根M2排线(Track)。于是,将阻断的排线数量从1开始逐步增加到2,3 。并以此为条件,试做了M1到M3,且测量了超级导孔的特性。

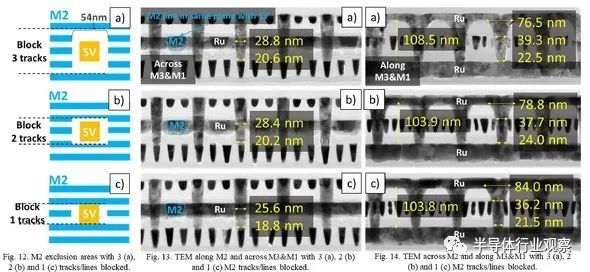

改变阻断的排线数量后,电子显微镜下观察试做的具有多层排线结构布局图案和断面。左边为阻断的M2的排线数量。从上往下依次为3,2,1 。中间和右边为排线结构的断面图,分别对应左边的被阻断的排线的数量。中间为与M2平行的M3和M1的断面图。右端为与M1和M3平行的M2的断面图。图像中间的黄色数值为超级导孔的各部分的尺寸

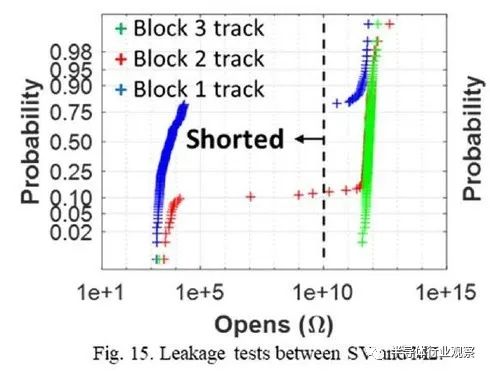

尤其受到重视的是超级导孔和M2绝缘电阻。测量了绝缘电阻(泄露电流)后发现,当一根M2的线路被阻断时,75%的超级导孔发生了短路不良问题。即使两根线路被阻断,也有10%的超级导孔发生了短路问题。当被阻断的线路为3时,短路问题不再那么明显。

超级导孔和M2的绝缘电阻。纵轴为累积概率(Cumulative Probability),横轴为电阻值

由上图可知,至少要阻断M2的三根线路,此外,如上文所述,当被阻断的线路为 4或者5时,就会影响排线布局。目前来看,三根是最理想的数量。

将阻断了M2的三根线路的超级导孔的电阻(导孔电阻)与AR比为3的叠加导通孔(Stacked Via)的电阻比较后发现,超级导孔的导孔电阻中央值较叠加导通孔下降了1/2.4,实现了大幅度的减少。超级导孔有望成为减少导孔电阻的一项关键技术。

利用开尔文连接法(Kelvin )测定各种导孔的电阻值结果。阻断M2的三根线路的超级导孔(SV)的电阻值较叠加导通孔(AR比为3)降低了1/2.4

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。