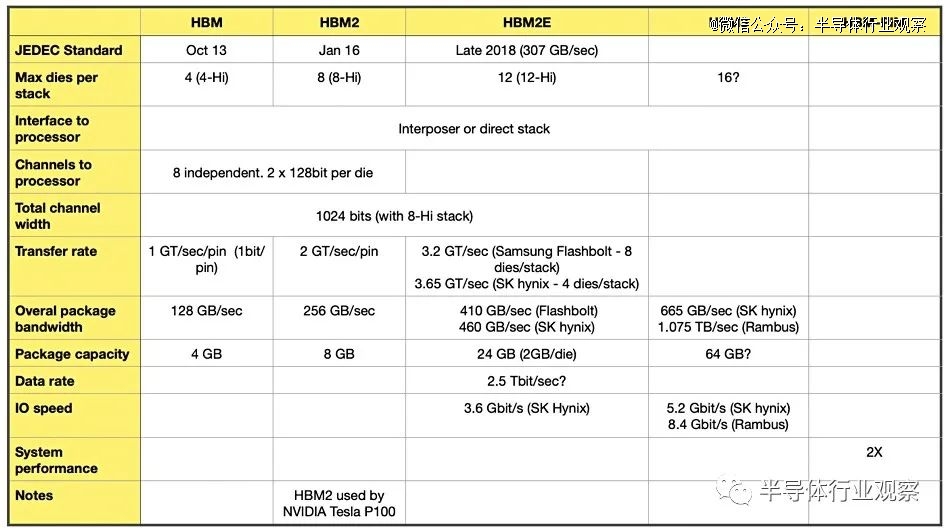

高带宽内存(High-bandwidth memory:HBM)已经存在了大约十年,在其不断发展的过程中,它的速度稳步提高,数据传输速率从 1 GT/s(最初的 HBM)开始,达到 9 GT/s 以上(即将推出的 HBM3E)。这使得带宽在不到 10 年的时间内实现了令人印象深刻的跃升,使 HBM 成为此后投放市场的全新 HPC 加速器类别的重要基石。

但随着内存传输速率的提高,尤其是在 DRAM 单元的基础物理原理没有改变的情况下,这一速度也越来越难以维持。因此,对于 HBM4,该规范背后的主要内存制造商正计划对高带宽内存技术进行更实质性的改变,从更宽的 2048 位内存接口开始。

01 HBM 4,迎来革命性改变

HBM 的当前 1024 位内存接口被设计为宽但慢的内存技术,具有以相对适中的时钟速度运行的超宽接口,已成为该技术的一个决定性特征。与此同时,为了不断提高内存带宽,其适度的时钟速度变得越来越不那么适度。到目前为止,这种方法一直有效,但随着时钟速度的提高,高度并行内存面临着与 GDDR 和其他高度串行内存技术相同的信号完整性和能效问题的风险。

因此,对于下一代技术,组织者正在考虑再次加宽,将 HBM内存接口的宽度进一步扩展至 2048 位。而且,出于多种技术原因,他们打算在不增加 HBM 内存堆栈占用空间的情况下实现这一目标,从而实质上使下一代 HBM 内存的互连密度加倍。最终结果将是一种具有比当今 HBM 更宽的内存总线的内存技术,为内存和设备供应商提供了进一步提高带宽而无需进一步提高时钟速度的空间。

按照计划,这将使 HBM4 在多个层面上实现重大技术飞跃。

例如在 DRAM 堆栈方面,2048 位内存接口将需要显著增加穿过内存堆栈的硅通孔数量。同时,外部芯片接口需要将凸块间距缩小到远低于 55 微米,同时显著增加微凸块总数(HBM3 目前的(大约)3982 个凸块数量)。

内存制造商表示,他们还将在一个模块中堆叠多达 16 个内存芯片,这为该技术增加了一些额外的复杂性。所谓的 16-Hi 堆叠。(HBM3 技术上也支持16-Hi 堆栈,但到目前为止还没有制造商实际使用它)这将使内存供应商能够显著增加其 HBM 堆栈的容量,但它在连接更多数量的 DRAM 时带来了新的复杂性没有错误地死亡,然后保持生成的 HBM 堆栈适当且一致地短。

所有这一切反过来都需要芯片制造商、内存制造商和芯片封装公司之间更加密切的合作,以使一切顺利进行。

台积电设计基础设施管理主管 Dan Kochpatcharin 在阿姆斯特丹举行的台积电 OIP 2023 会议上发表讲话时表示:“因为他们没有将速度加倍,而是使用 HBM4 将[接口]引脚加倍。这就是为什么我们正在推动确保我们与所有三个合作伙伴合作,[使用我们先进的封装方法]验证他们的 HBM4,并确保 RDL 或中介层或两者之间的任何内容都可以支持 [HBM4] 的布局和速度。因此,我们与三星、SK海力士和美光携手合作。”

由于系统级封装 (SiP) 设计变得越来越大,并且先进芯片封装支持的 HBM 堆栈数量不断增加(例如 6 倍掩模版尺寸中介层和封装上具有 12 个 HBM 堆栈的芯片),因此芯片封装变得越来越复杂。为了确保一切继续协同工作,台积电正在推动芯片和内存设计人员采用设计技术协同优化(DTCO)。这也是全球*的代工厂最近组织 3DFabric 内存联盟的一个重要原因,该计划旨在促进 DRAM 制造商和台积电之间的密切合作,以实现下一代解决方案,该解决方案将封装大量逻辑晶体管和先进存储。

除此之外,台积电的 3DFabric 内存联盟目前正在致力于确保 HBM3E/HBM3 Gen2 内存与 CoWoS 封装配合使用、12-Hi HBM3/HBM3E 封装与高级封装、用于 HBM PHY 的 UCIe 以及无缓冲区 HBM(一种技术)兼容。由三星牵头)。

总体而言,台积电上周的评论让我们对下一代高带宽内存有了*的了解。尽管如此,有关 HBM4 的其他技术细节目前仍然相当缺乏。美光科技今年早些时候表示 ,“HBMNext”内存将于 2026 年左右上市,每个堆栈的容量将在 36 GB 至 64 GB 之间,每个堆栈的峰值带宽将达到 2 TB/s 或更高。所有这些都表明,即使转向更宽的内存总线,内存制造商也不会放弃 HBM4 的内存接口时钟速度。

02 HBM 4争夺战,即将打响

正如上文所说,HBM市场主要由三星、SK海力士和美光三家机构把持。按照市场追踪机构TrendForce的数据显示,截至2022年,该公司在全球HBM市场中占领了50%的份额,三星电子紧随其后,占40 %,其次是美光科技公司占10%。

现在,他们也正在HBM 4上火力全开,明争暗斗。

近日全球*存储芯片制造商三星电子公司的一位高管在一篇博客文章内表示,公司目标是在2025年推出第六代*性能高带宽内存4(HBM4)DRAM芯片,以赢得快速增长的人工智能芯片领域迫切激烈战争的主导权。

该高管表示,2016年,三星将业界*用于高性能计算(HPC)的高带宽内存(HBM)商业化,并寻求扩大AI内存市场的机会。一年后,即 2017 年,三星推出了 8 层堆叠 HBM2。与当时最快的 GDDR5 内存相比,HBM2 的速度提高了八倍。通过 HBM2,三星成功展示了 3D 堆叠技术的可行性,该技术将继续成为新 HPC/AI 领域的重要组成部分。随后,三星量产了 HBM2E 和 HBM3,并开发了 9.8 Gbps HBM3E,我们很快就会开始向客户提供样品,以丰富 HPC/AI 生态系统。

展望未来,HBM4 预计将于 2025 年推出,其技术针对正在开发的高热性能进行了优化,例如非导电薄膜 (NCF:non-conductive film) 组装和混合铜接合 (HCB:hybrid copper bonding )。

值得一提的是,因为三星于 2023 年初成立了 AVP(高级封装)业务团队,以加强先进封装技术并*限度地发挥各业务部门之间的协同效应。除了 HBM 之外,三星还将提供先进的定制交钥匙封装服务,包括 2.5D 和 3D 先进封装解决方案,非常适合 HPC 和 AI 时代。

来到SK Hynix 方面,据官方资料介绍,2014年,SK海力士与AMD联合开发了全球*硅通孔(TSV, Through Silicon Via)HBM产品。两家公司还联合开发了高带宽三维堆叠存储器技术和相关产品。SK海力士还是首家开始批量生产HBM2E的存储器供应商,HBM2E是HBM2的扩展版本。HBM2E开发团队在规划阶段就立志升级产品规格,这也是SK海力士维持市场*地位的关键。SK海力士在2021年10月开发出全球*HBM3,持续巩固其市场*地位。HBM3的容量是HBM2E的1.5倍,由12个DRAM芯片堆叠成,总封装高度相同,适用于AI、HPC等容量密集型应用。

在七月的一场投资者分析会上,SK海力士还透露了其下一代产品的具体路线图。他们将第六代HBM产品HBM4的生产目标定为2026年。目前,SK海力士已确定明年上半年为其下一代产品HBM3E的量产时间。

从技术上来说,有关于“Mass Rework Molded Underfill”的解释,这是SK海力士开发的*个封装技术,涉及在芯片上堆叠芯片。SK海力士公开表示,他们将把下一代后处理技术“混合键合”应用于HBM4产品。与现有的“非导电膜”工艺相比,它提高了散热效率并减少了布线长度,从而实现了更高的输入/输出密度。这会将当前的* 12 层增加到 16 层。

美光作为HBM市场的后起之秀,也在紧追满赶两位韩国存储巨头。

在今年七月,美光科技公司宣布,已开始提供业界* 8 高(8-high ) 24GB HBM3 Gen2 内存样品,其带宽和引脚数超过 1.2TB/s速度超过 9.2Gb/s,比当前发售的 HBM3 解决方案提高了 50%。美光 HBM3 Gen2 产品的每瓦性能比前几代产品提高了 2.5 倍。

美光表示,公司的高带宽内存 (HBM) 解决方案的基础是美光业界*的 1β (1-beta) DRAM 工艺节点,该节点允许将 24Gb DRAM 芯片组装到行业标准封装尺寸内的 8 高立方体中。此外,美光的 12 高堆栈(容量为 36GB)将于 2024 年*季度开始提供样品。

按照美光所说,与现有的竞争解决方案相比,公司在给定堆栈高度下提供的容量增加了 50%。美光的 HBM3 Gen2 性能功耗比和引脚速度改进对于管理当今人工智能数据中心的极端功耗需求至关重要。功率效率的提高是可能的,因为美光科技的进步包括硅通孔 (TSV) 比竞争对手的 HBM3 产品增加一倍、通过金属密度增加五倍来降低热阻抗以及节能数据路径设计。

关于未来的布局,美光披露了暂名为HBMnext的下一代 HBM 内存,这有可能将是其HBM 4。

美光预计M其 HBMNext 将提供 36 GB 和 64 GB 容量,这意味着多种配置,例如 12-Hi 24 Gb 堆栈 (36 GB) 或 16-Hi 32 Gb 堆栈 (64 GB) 。至于性能,美光宣称每个堆栈的带宽为 1.5 TB/s – 2+ TB/s,这意味着数据传输速率超过 11.5 GT/s/pin。

写在最后:

根据SK海力士预测,AI芯片的繁荣带动HBM市场到2027年将出现82%的复合年增长率。分析师也认为,预计明年HBM市场将比今年增长一倍以上。三星电子DRAM产品与技术执行副总裁Hwang Sang-joon在KIW 2023上表示:“我们客户当前的(HBM)订单决定比去年增加了一倍多。”三星芯片负责业务的设备解决方案部门总裁兼负责人 Kyung Kye-hyun 在公司会议上更表示,三星将努力控制一半以上的 HBM 市场。三星内存业务执行副总裁 Jaejune Kim 对分析师表示,该公司将在 2023 年至 2024 年间将其 HBM 产能增加一倍。

在三星的强势出击下,对于SK海力士和美光,需要运筹帷幄,才能避免在未来的HBM竞争中掉队。

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。