据台媒经济日报报道,台积电冲刺CoWoS先进封装布局,最新传出又要在南科三期盖两座CoWoS新厂,投资金额估逾2,000亿元。加计台积电正在嘉科园区如火如荼建置的CoWoS新厂,业界预期,台积电短期内总计将扩充八座CoWoS厂,其中,南科至少有六座,以实际扩产行动棒打CoWoS砍单传闻。

对于相关传闻,南科管理局表示,台积电确实有提出租地申请,惟不便透露厂商的开发计划。台积电方面,董事长魏哲家上周于法说会已明确释出“持续扩增CoWoS产能”的讯息。业界研判,台积电再次砸重金盖CoWoS新厂,透露来自英伟达等大客户高速运算(HPC)相关订单比预期更旺。

近期英伟达砍单台积电CoWoS的传闻甚嚣尘上,英伟达执行长黄仁勋日前旋风式访台,直言:“并没有缩减CoWoS产能需求,反而还要增加产能,并转换为多一些对CoWoS-L的产能需求。”魏哲家日前于法说会也说,“外面谣言多,公司正持续扩产,以满足客户需求。”

知情人士透露,台积电这次在南科盖CoWoS新厂,将落脚南科三期,土地面积高达25公顷,比嘉科厂区约20公顷更大,以嘉科CoWoS新厂投资约2,000亿元计算,台积电此次在南科三期投资额也将「比照办理」、自2,000亿元起跳。

知情人士指出,魏哲家喊话持续扩充CoWoS产能,绝 对不是说说而已,而是以最高效率动起来,最快3月就会取得南科三期这块25公顷土地,将兴建二座CoWoS新厂,以及一栋办公大楼。

建厂进度方面,供应链透露,台积电在今年1月中旬向南科管理局提出租地简报,获正向回应,该公司采购单位即已第 一时间启动建厂计划。根据消息,台积电预计3月开始整地,依据以往建厂的进度推估,两座南科三期CoWoS新厂将于2026年4月即可完工,并有望开始装机。

AI强劲需求带动下,供应链统计,台积电短期内规划盖八座CoWoS新厂,包括嘉义一期已建的二座,原本群创四厂也将改建为二座;另外,嘉义二期原规划建两座,不过,因嘉义二期因最快也要到明年1月才能交地,而南科三期马上可以交地,因此台积电建构规划转向。台积电已决定向南科先行租用南科三期土地兴建二座CoWoS新厂。至于最后两座要落脚何处,目前仍在评估中。

CoWoS产能,大增

台积电在台湾各地兴建新晶圆厂,扩大产能,以满足不断增长的 CoWoS 和 AI 市场需求。

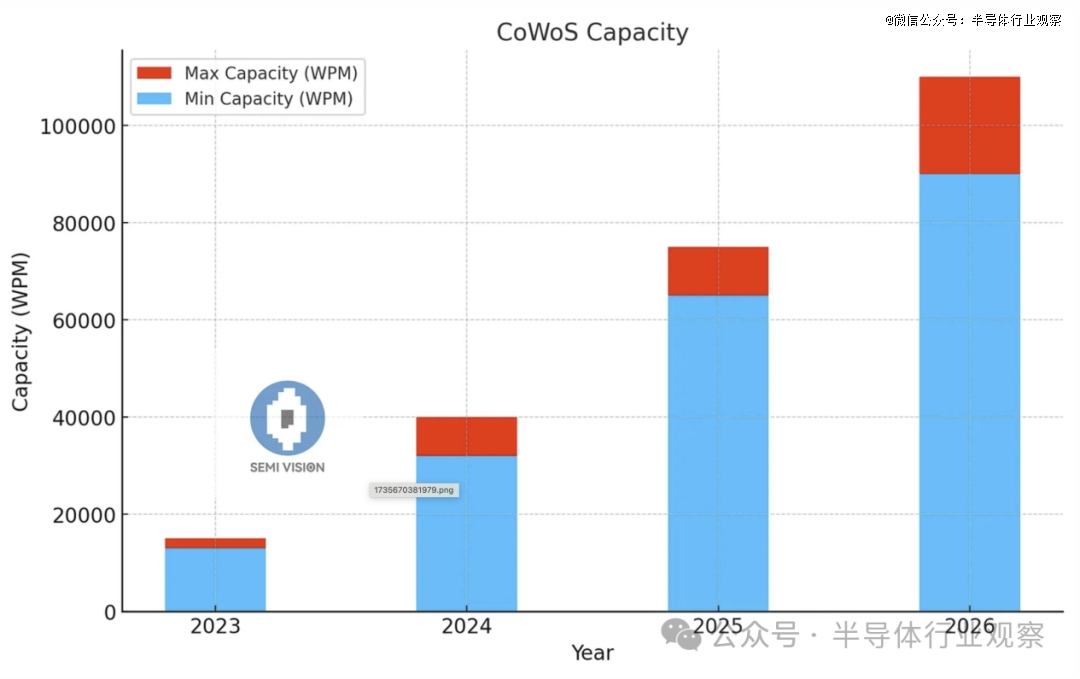

Total CoWoS Capacity (WPM= Wafer Per Month):

2023: 13,000 ~ 16,000 WPM

2024: 35,000 ~ 40,000 WPM

2025e: 65,000 ~ 75,000 WPM

2026e: 90,000 ~ 110,000 WPM

台积电先进封装CoWoS(晶圆上芯片)技术的快速增长受到以下几个关键因素的推动:

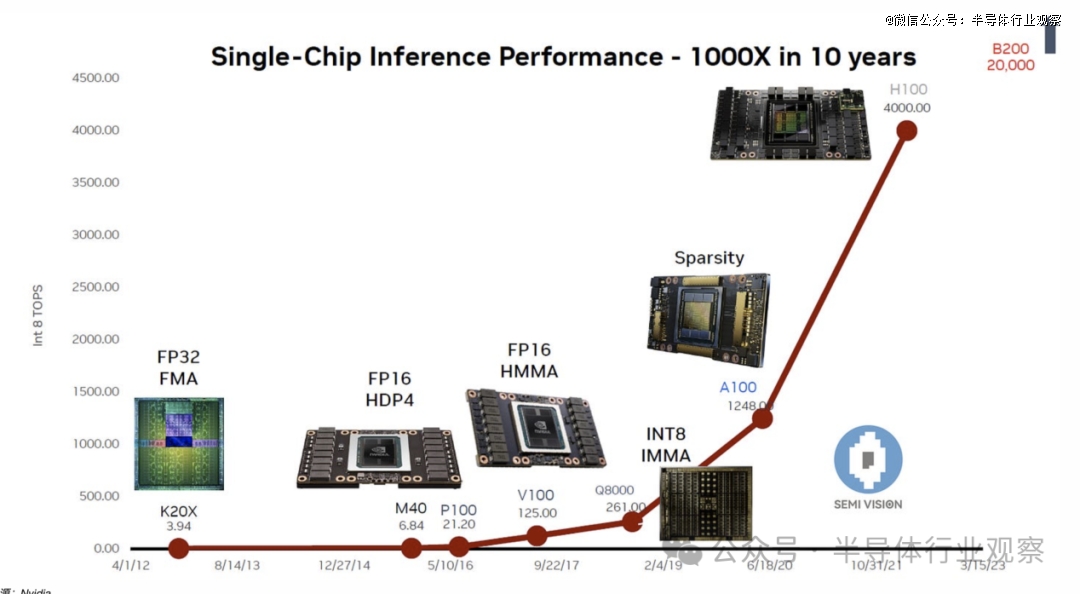

对高性能计算 (HPC) 的需求:对高级 AI、机器学习和数据中心应用的需求日益增长,需要像 CoWoS 这样的创新半导体封装技术来处理更高的计算工作负载。

系统集成方面的进步:CoWoS 能够在单个基板上集成多个芯片、内存和逻辑封装,满足对更高带宽、更低延迟和更高能效的日益增长的需求。

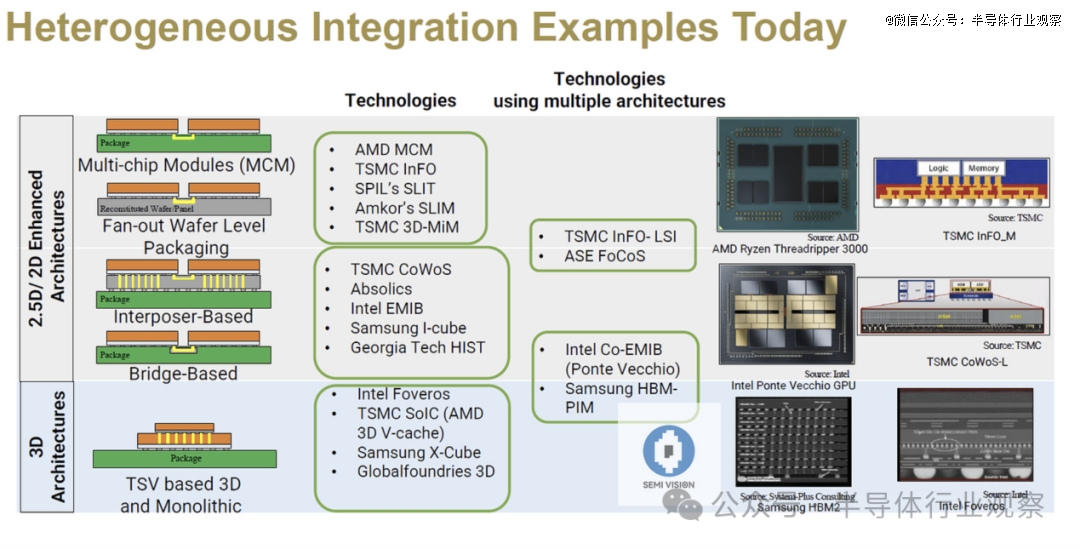

2.5D 封装市场不断增长:CoWoS 是 2.5D 集成领域的领 导者,它结合了高密度互连和大规模芯片集成,以提高整体系统性能。

半导体设计复杂性不断增加:随着半导体尺寸缩小变得越来越具有挑战性,CoWoS 提供了一种可扩展的解决方案,用于生产满足现代电子产品需求的异构集成芯片。

其他 2D/2.5D 封装供应商:ASE VIPack、Absolics、英特尔 EMIB、三星 I-cube、Amkor、SPIL。

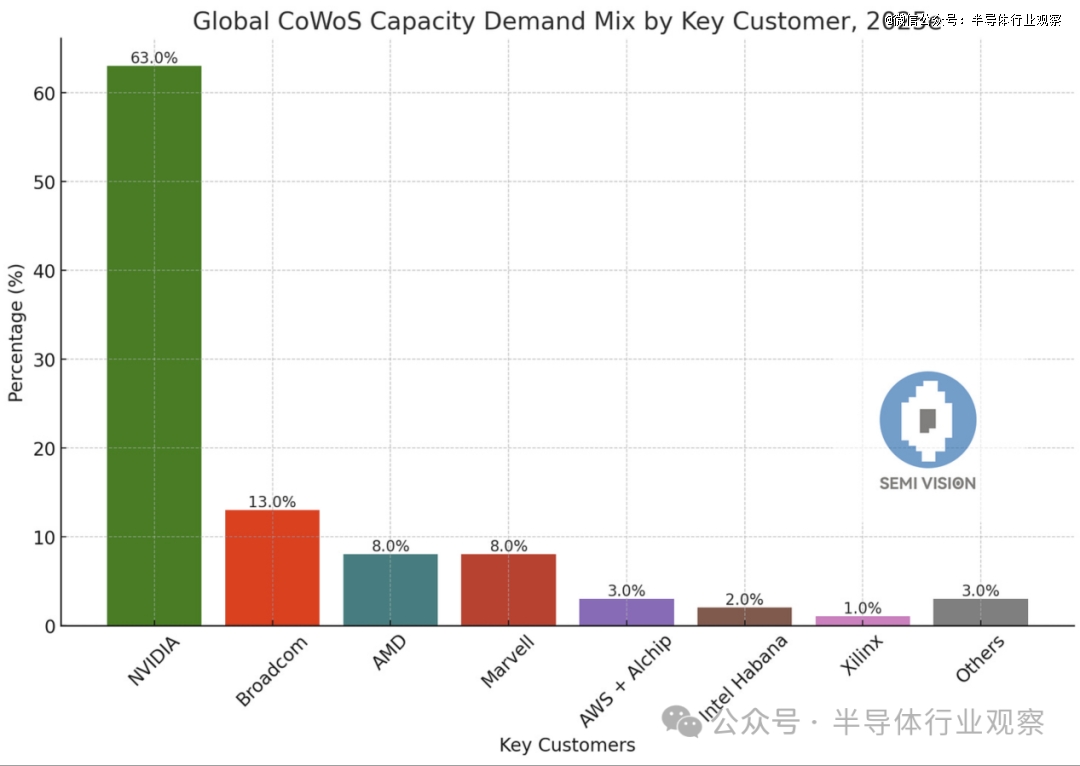

NVIDIA 领跑 2025 年全球 CoWoS 容量需求份额:

NVIDIA在容量需求方面占据主导地位,占据总需求的63%,表明其在采用 CoWoS 技术方面的领导地位。

紧随其后的是博通,占13%,是 CoWoS 需求的第二大贡献者,尽管远远落后于 NVIDIA。

AMD和Marvell各占8%,并列第三,表明两家公司对这项技术的兴趣相当。

其他贡献者包括AWS + Alchip(3%)、英特尔(2%)、Xilinx(1%)和其他(3%),所占份额要小得多,表明他们对 CoWoS 容量的依赖相对有限。

NVIDIA 对 CoWoS 技术的高需求主要源于其在开发高性能计算和人工智能 (AI) 硬件方面的领导地位。这种需求的主要原因包括:

适用于 AI 和 HPC 的先进封装:CoWoS 技术使 NVIDIA 能够将多个高带宽内存 (HBM) 芯片与其 GPU 封装在单个基板上。这对于需要大量计算能力和内存带宽的 AI 训练、推理和 HPC 至关重要。

人工智能和机器学习蓬勃发展:NVIDIA 的 GPU 是全球人工智能和机器学习系统的核心。各行各业人工智能应用的快速增长大大增加了对 CoWoS 等先进封装解决方案的需求,以满足性能需求。

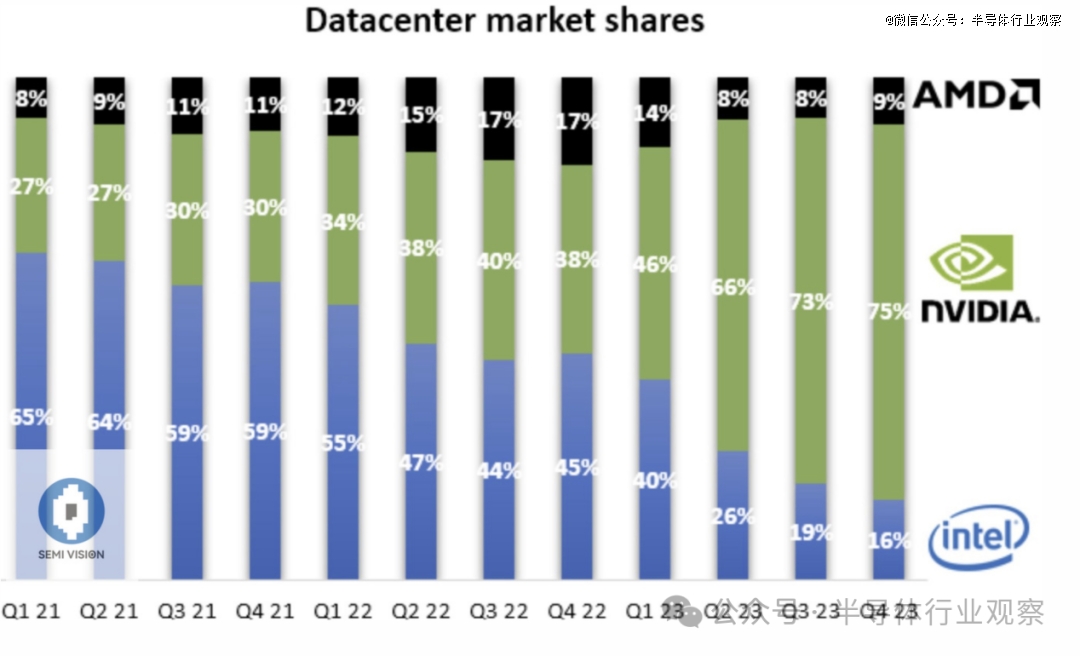

数据中心领导地位:NVIDIA 主导数据中心市场,其 GPU 用于大规模 AI 训练和推理任务。CoWoS 技术可实现更高的性能和能效,是 NVIDIA 数据中心产品必不可少的技术。

Chiplet 架构:CoWoS 支持 NVIDIA 向基于 Chiplet 的架构迈进,从而实现模块化设计和更好的可扩展性。这对于其下一代产品尤其重要。

关键行业的需求:人工智能、大模型、自动驾驶汽车和科学研究等行业严重依赖 NVIDIA GPU 来实现人工智能驱动的解决方案,进一步推动了对 CoWoS 技术提供尖端性能的需求。

CoWOS技术是什么?

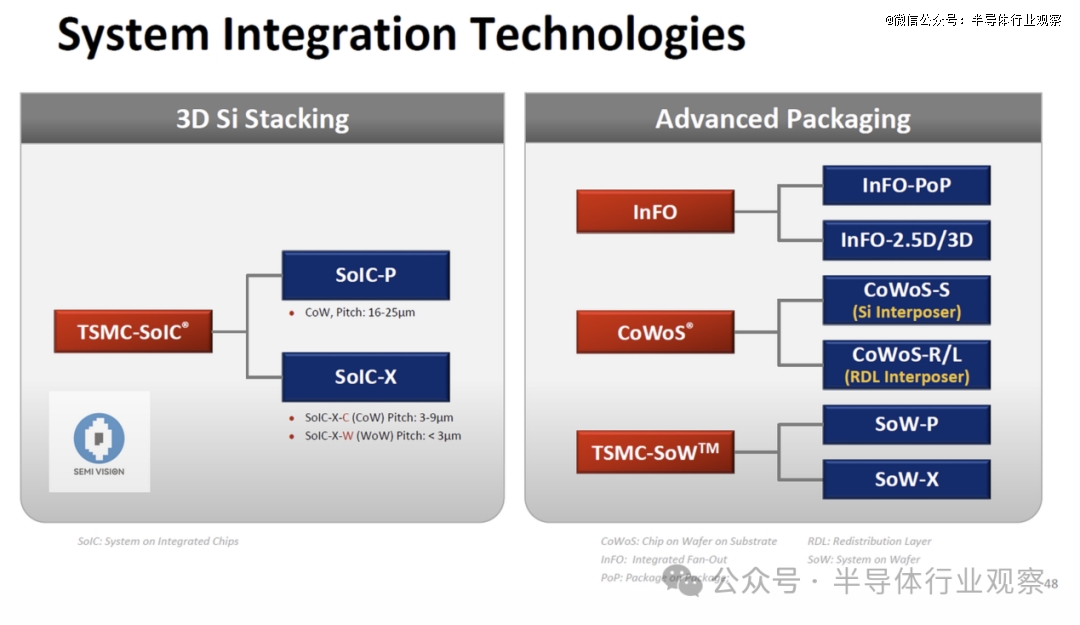

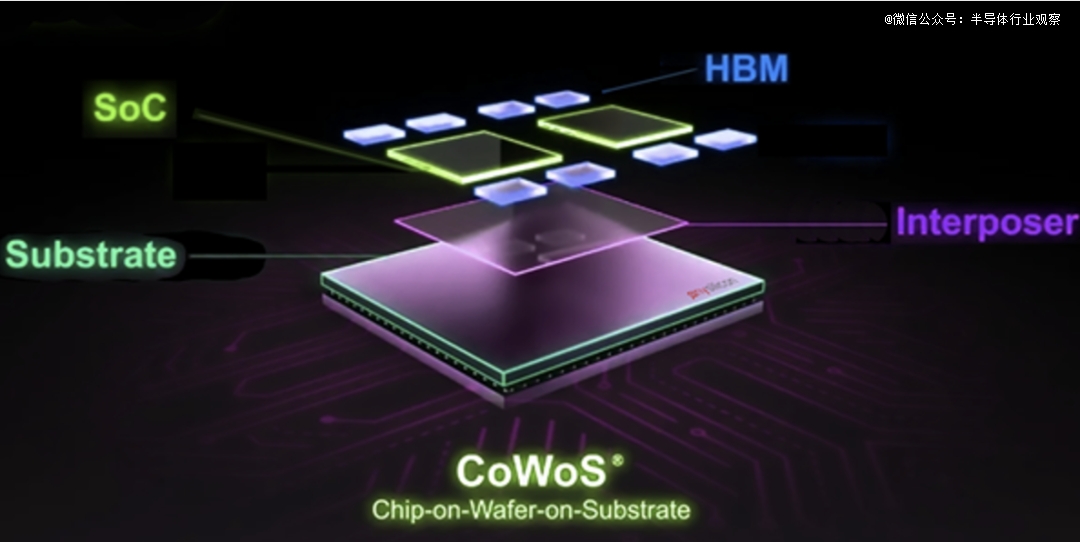

晶圆上芯片 (CoWoS:Chip-on-wafer-on-substrate)是一种先进的封装技术,具有封装尺寸更大和 I/O 连接更多等优势。它允许 2.5D 和 3D 组件堆叠,以实现同质和异构集成。以前的系统面临内存限制,而当代数据中心则使用高带宽内存 (HBM) 来增强内存容量和带宽。CoWoS 技术允许在同一 IC 平台上异构集成逻辑 SoC 和 HBM。

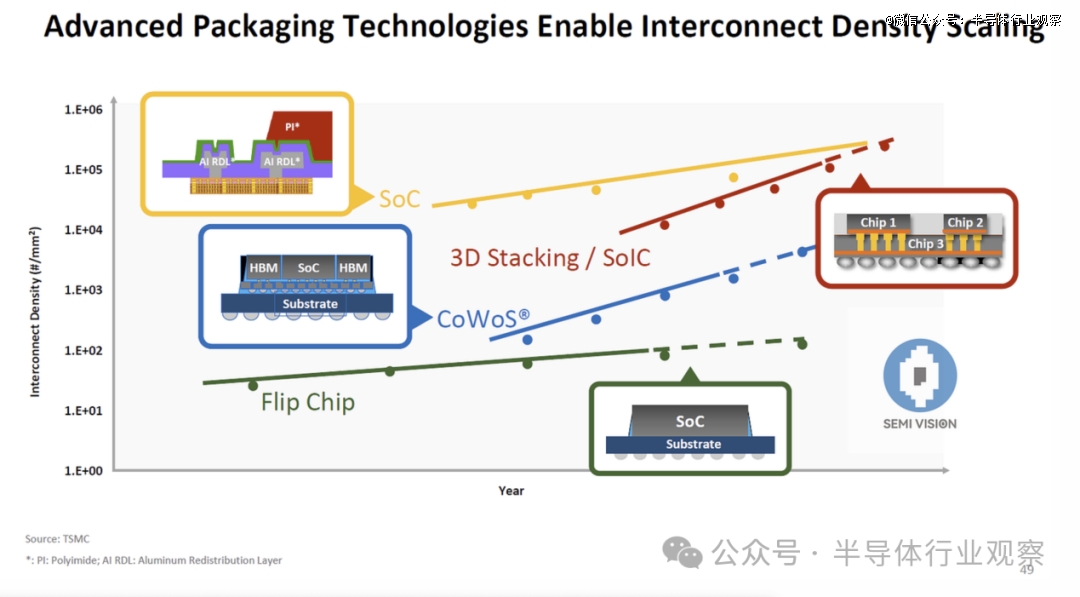

CoWoS 架构包含 2.5D 水平堆叠和 3D 垂直堆叠配置,彻底改变了传统的芯片封装模式。这种创新方法允许逐层堆叠各种处理器和内存模块,从而创建相互连接以形成一个有凝聚力的系统的小芯片。通过利用硅通孔 (TSV) 和微凸块,与传统的 2D 封装方法相比,CoWoS 可以缩短互连长度、降低功耗并增强信号完整性。

从实际角度来看,CoWoS 技术能够将 GPU 和 AI 加速器等高级处理单元与高带宽内存 (HBM) 模块无缝集成。这种集成对于 AI 应用尤其重要,因为在这些应用中,大规模计算能力和快速数据访问至关重要。通过将处理和内存元件放在近距离内,CoWoS 可以最 大限度地减少延迟并最 大限度地提高吞吐量,从而为内存密集型任务带来前所未有的性能提升。

CoWoS 技术具有多种优势:

规模化和更高集成度:传统上,按照摩尔定律对晶体管进行规模化有助于满足提高性能的需求。然而,事实证明,这对于高性能计算 (HPC)、人工智能甚至图形处理单元 (GPU) 等现代应用而言是不够的。CoWoS 允许在同一基板上堆叠芯片,从而减少同质或异构逻辑 SoC 之间以及 HBM 之间的互连延迟。

增强热管理:硅中介层和有机中介层的使用大大增强了堆叠集成电路的热管理能力。这直接提高了整个系统的可靠性和使用寿命,同时最 大限度地降低了热节流的风险。

提高电源完整性:中介层中的电源/接地网络使用 RDL,并结合深槽电容器 (DTC),不会损害高速应用和内存密集型应用的电源完整性。

尺寸和成本降低:CoWoS 技术有助于在同一中介层和基板上安装多个逻辑 SoC 和 HBM。这与传统封装技术形成鲜明对比,传统封装技术过去需要将多个逻辑 SoC 安装在印刷电路板 (PCB) 上,并在封装中进行必要的连接。这导致封装尺寸更大,并增加了材料成本和制造费用。CoWoS 封装总体上更小,更具成本效益。

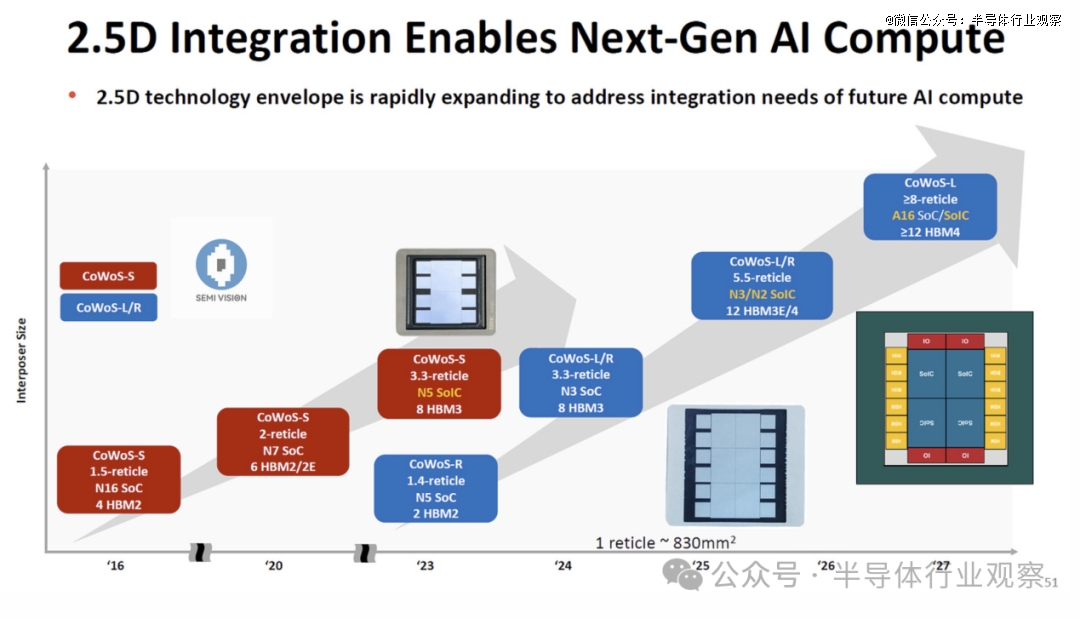

据介绍, 目前有CoWoS-S、CoWoS -L 和 CoWoS -R三个平台。不同的互连选项提供更大的灵活性集成,以满足性能目标。

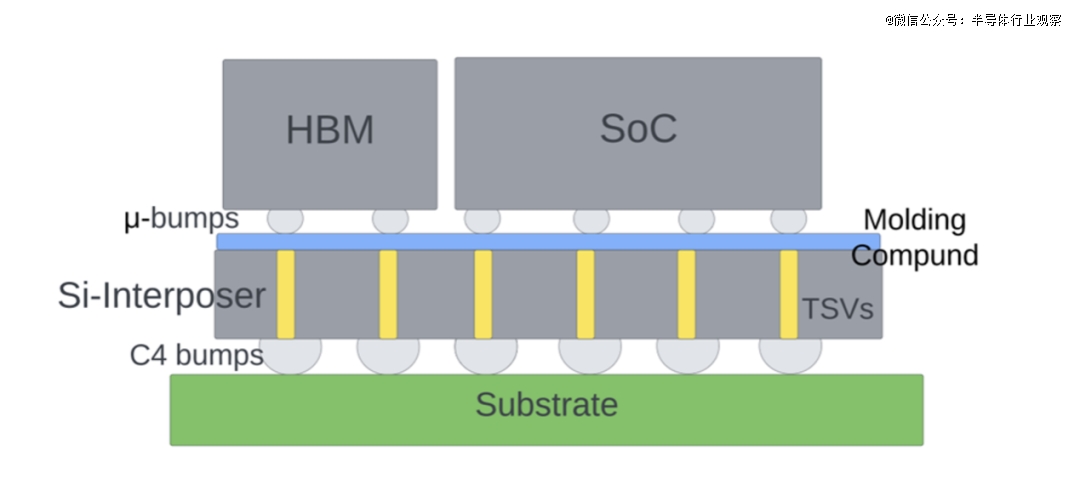

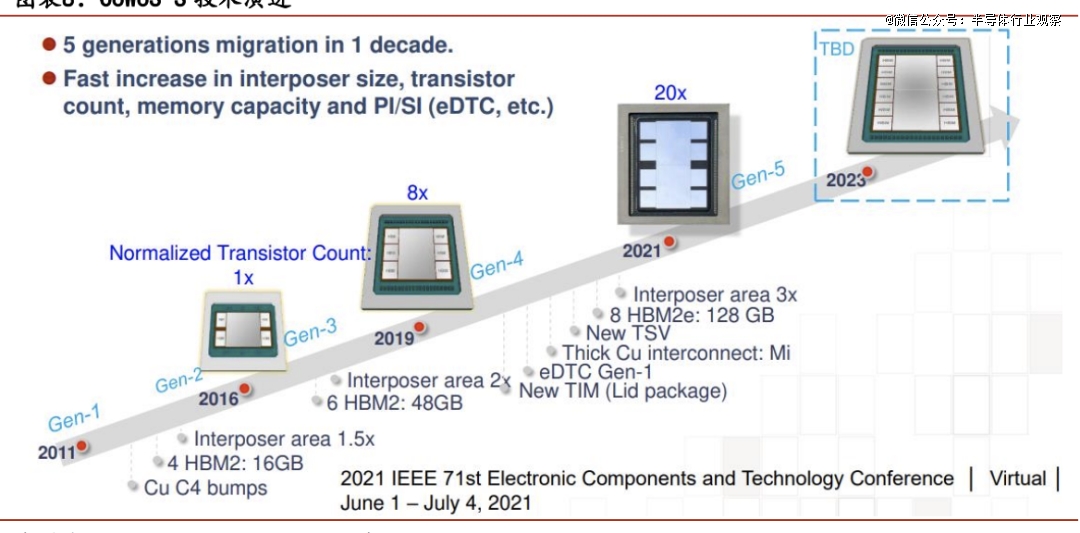

据中邮证券的报告,CoWoS-S(Silicon Interposer)即 2011 年首次亮相的用硅(Si)衬底作为中 介 层 的 先 进 封 装 技 术 ( chip-on-wafer-on-substrate with silicon interposer)和TSV,提供广泛的中介层尺寸、HBM 立方体数量和封装尺寸,可以实现大于 2X 的光罩尺寸(1,700mm2),中介层集成了*的 SoC 芯片和四个以上的HBM2/HBM2E 立方体。在过去,“CoWoS”一般即指以硅基板作为中介层的先进封装技术。

报告进一步指出,CoWoS-S 从 2011 年的第 一代升级到 2021 年的第五代,后续的第六代技术将会在基板上封装 2 颗运算核心,同时可以板载多达 12 颗 HBM 缓存芯片。第五代 CoWoS-S 技术使用了全新的 TSV 解决方案,更厚的铜连接线,晶体管数量是第 3 代的 20 倍。它的硅中介层扩大到 2500mm2,相当于 3 倍光罩面积,拥有 8 个 HBM2E 堆栈的空间,容量高达 128 GB。并且,台积电以 Metal Tim形式提供最新高性能处理器散热解决方案,与第 一代 Gel TIM 相比,封装热阻降低至 0.15 倍。

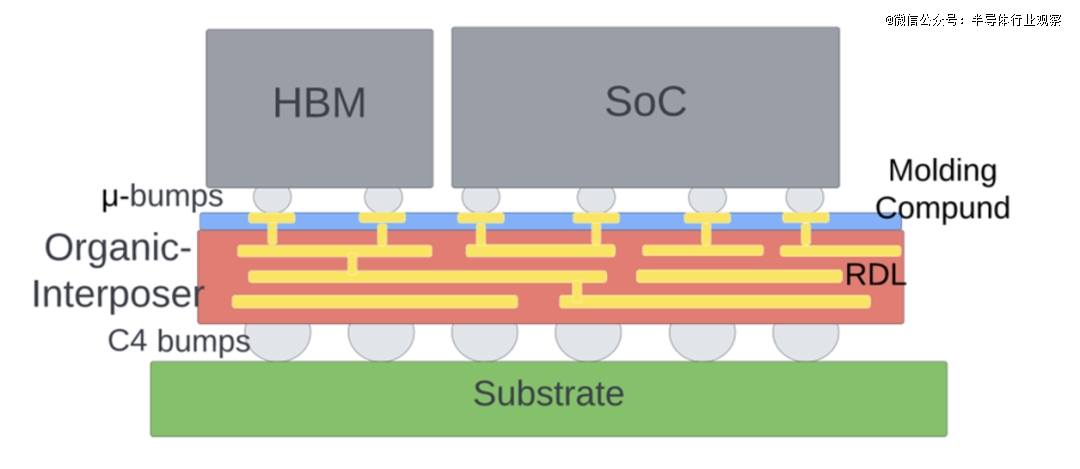

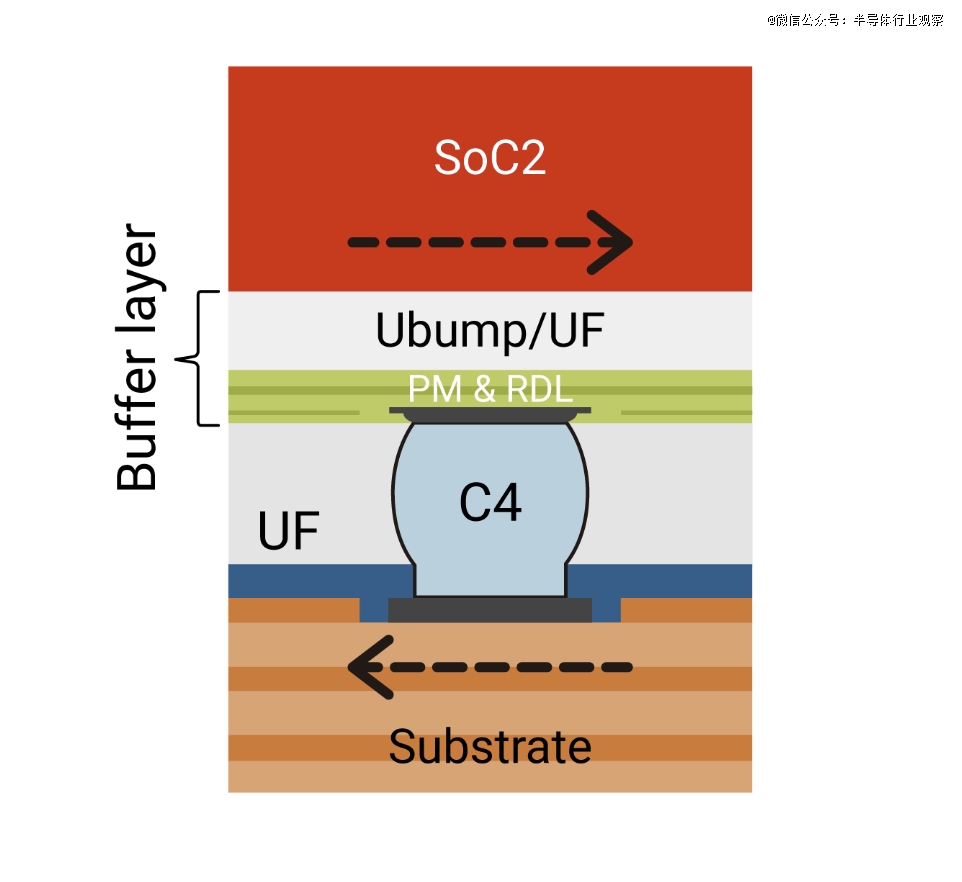

CoWoS-R则使用有机中介层取代了 CoWoS-S 的硅中介层。有机中介层具有细间距 RDL,可在 HBM 和芯片之间甚至芯片和基板之间提供高速连接。与 CoWoS-S 相比,CoWoS-R 提供了*的可靠性和良率,因为有机中介层本身具有柔韧性,可充当应力缓冲器,并减轻由于基板和中介层之间的热膨胀系数不匹配而引起的可靠性问题。

按照台积电所说,CoWoS -R 的主要特点包括:

1、用于布线的 RDL 中介层最多包含 6 个铜层,间距最小为 4μm(线宽/间距为 2μm)。

2、RDL 互连提供良好的信号和电源完整性,并采用较低的 RC 值布线,以实现高数据传输率。共面接地-信号-接地-信号-接地 (GSGSG) 和具有六个 RDL 互连的层间接地屏蔽可提供卓 越的电气性能。

3、由于 SoC 和相应基板之间的热膨胀系数 (CTE) 不匹配,RDL 层和 C4/底部填充 (UF) 层提供了出色的缓冲。C4 凸块区域的应变能量密度大大降低。

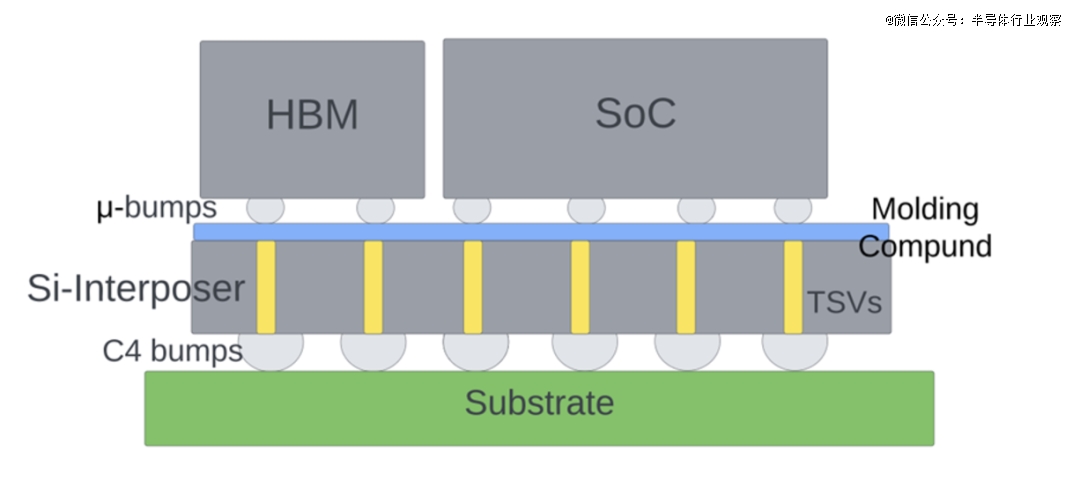

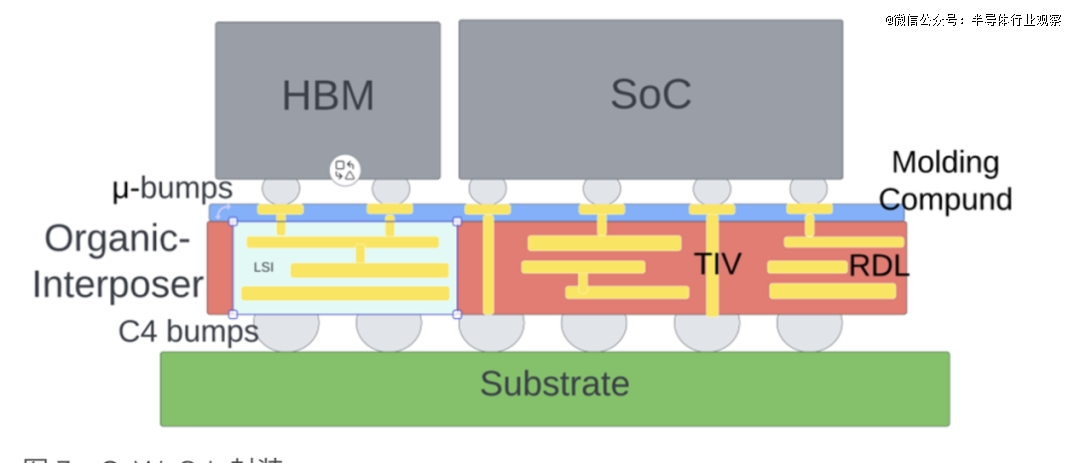

CoWoS-L则使用局部硅互连 (LSI) 和 RDL 中介层一起形成重组中介层 (RI)。除了 RDL 中介层之外,它还以硅通孔 (TSV) 的形式保留了 CoWoS-S 的吸引力。这还可以缓解由于在 CoWoS-S 中使用大型硅中介层而产生的产量问题。在一些实现中,它还可以使用绝缘通孔 (TIV) 代替 TSV 来最 大限度地减少插入损耗。

CoWoS -L 的主要特点包括:

1、LSI 芯片用于通过多层亚微米铜线实现高布线密度芯片间互连。LSI 芯片可以在每个产品中采用各种连接架构,例如片上系统 (SoC) 到 SoC、SoC 到芯片组、SoC 到高带宽内存,并且可以在多种产品中重复使用。相应的金属类型、层数和间距与 CoWoS -S 的产品一致。

2、基于成型的中介层在正面、背面和传输信号和电源的 InFO 通孔 (TIV) 上具有较宽的 RDL 层间距,可在高速传输过程中降低高频信号的损耗。

3、能够在 SoC 芯片下方集成独立嵌入式深沟槽电容器等附加元素,以改善电源管理。

总而言之,CoWoS-L 是一种芯片后组装工艺,因为先制造中介层,然后再在上面堆叠晶圆芯片。中介层是 CoWoS 技术中的关键原材料之一,因为中介层上安装了多个晶圆芯片(如 SoC、HBM 等),并且它能够实现芯片之间的高效连接和通信。中介层制造完成后,下一步就是在晶圆芯片中创建绝缘通孔 (TIV)。

然后将已知合格的裸片 (KGD) 安装在晶圆上。裸片和 TIV 之间的间隙用模塑料填充,然后采用 CMP 工艺获得平坦表面。

下一步,制造两个 RDL 层:一个位于中介层正面,通过 μ-bump 连接晶圆和基板。

中介层背面的第二条 RDL 通过 C4 凸块连接中介层和基板。

除此之外,CoWoS-L 技术还采用深沟槽电容器 (DTC),可提供高电容密度,从而提高系统的电气性能。这些电容器充当电荷储存器,并在运行高速计算应用程序时满足瞬时电流需求。

写在最后

在大力扩充封装产能的同时,台积电还在加紧建设晶圆厂。

据报道,台积电持续扩大投资高雄,规划于P3 厂房东侧土地接续启动扩建计划,延续先进制程,发挥产能群聚综效,扩建的P4、P5 厂房预计2025 年动工。台积电表示,高雄厂按进度进行,配合政府程序。

台积电已规划在高雄建置3座晶圆厂,其中,P1、P2将生产2纳米制程芯片,P3厂房已启动建筑规划、执照申请及现地开工等作业,预计2026年办理竣工及申请使照,将生产2纳米或更先进制程芯片。

基于全球半导体产业急遽变动、国际竞争压力及产业制程全球布局考量,台积电有持续建厂扩充先进制程产能的迫切需求,规划于P3厂房东侧相邻的土地接续启动扩建计划。

在台积电高歌猛进的同时,我们只留下一个疑问,谁能挑战台积电?

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。