台积电最近在加利福尼亚州圣克拉拉举行了年度技术研讨会,演讲全面概述了它们的状态和即将到来的路线图,涵盖了工艺技术和先进封装开发的各个方面。本文将总结工艺技术更新的亮点。

魏哲家分享的一些信息

“今年是台积电成立 35 周年。1987 年我们成立,当时我们一共拥有 258 名员工,并发布了涵盖 3 种技术的 28 种产品;十年后,我们拥有 5,600 名员工,发布了涵盖 20 种技术的 915 款产品;到 2022 年,我们有 63,000 名员工,将发布 12,000 种产品,涵盖 300 项技术。”

“从 2018 年到 2022 年,12 英寸晶圆(当量)的年复合增长率超过 70%。特别是,我们看到‘big die’产品数量的显著增加。” (>500mm²)

“2021年,台积电北美业务板块出货量超过700万片,产品出货量超过5500件。有 700 个新产品流片 (NTO)。这部分占台积电收入的 65%。”

“我们的 gigafab 扩张计划通常包括每年增加两个新的‘阶段’——2017-2019 年就是这种情况。2020 年,我们开设了六个新阶段,包括我们的先进封装工厂。2021年有7个新阶段,包括台湾和海外的晶圆厂,也增加了先进封装产能。2022年将有5个新阶段,无论是在台湾还是在海外。”

N2晶圆厂:新竹Fab20

N3:台南Fab 18

N7和N28:高雄Fab22

N28:中国南京的Fab16

N16、N28 和专业技术:日本熊本的 Fab23(2024 年)

亚利桑那州的 N5(2024 年)

“统计全球已经安装的EUV光刻机系统中,台积电拥有了其中的 55%”

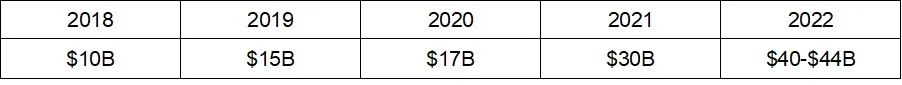

“我们将在 2022 年大幅扩大资本设备投资。”(下表突出显示了上限设备计划支出的大幅增长。)

“我们正在经历成熟工艺节点的制造压力。35 年来,我们从未在后续节点大规模生产后增加成熟节点的产能——但这种情况正在发生庄边。我们正在投资以提高我们 45nm 工艺的产能。” (后来,在与另一位台积电高管的问答环节中,有记者问道是否会在例如 90nm 或 65nm等其他成熟节点上执行产能扩张,他们给出的回应是:“不,扩张计划目前仅针对 45nm 节点。”)

“我们继续大力投资‘智能制造’,专注于精密过程控制、工具生产力和质量。每个 gigafab 每天处理 1000 万个调度订单,并优化工具生产力。每个 gigafab 每天都会生成 70B 的数据点以进行主动监控。”

在研讨会上,首次在展厅分配了一个特殊的“创新区”。重点介绍了一些初创公司最近提供的产品。台积电表示:“我们增加了支持投资,以帮助小公司采用我们的技术。有一个专门的团队专注于初创企业。对小客户的支持一直是重点。也许这个领域的某个地方将成为下一个英伟达。”

台积电的 12 个关键里程碑

1987 年,随着 PurePlay 商业模式的创建,台积电成立。

1999 年,台积电成为*家提供 0.18 微米铜技术的代工厂。

2001 年带来了*个代工参考设计流程。台积电花费了大量资金来创建我们今天享有的庞大 EDA 和 IP 生态系统。

2011 年,台积电将 HKMG 28nm 带入无晶圆生态系统。其他代工厂在 28nm 时步履蹒跚,因此这是台积电创纪录的节点。

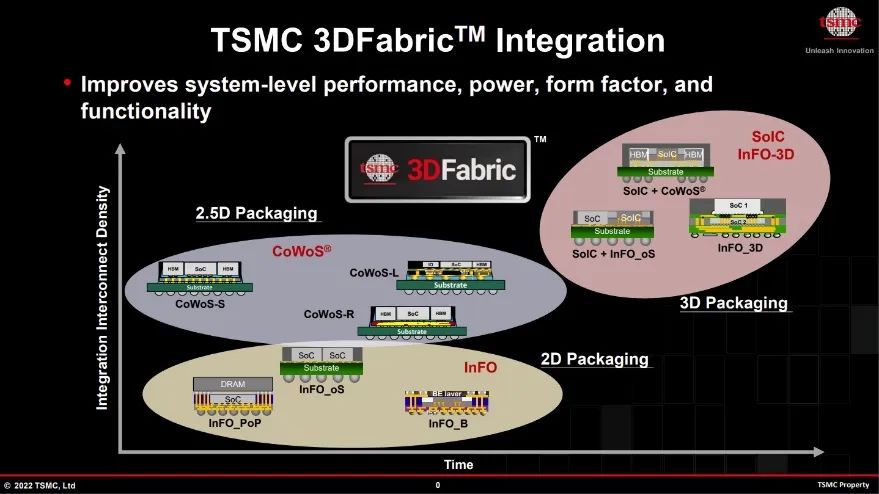

2012 年推出了CoWos,*款异构 3DIC test vehicle 。

2014 年,台积电交付了*款功能齐全的 FinFET 网络处理器,开启了今天台积电主导的 FinFET 时代。

2015 年台积电通过了先进的 3DIC 封装技术 InFo。

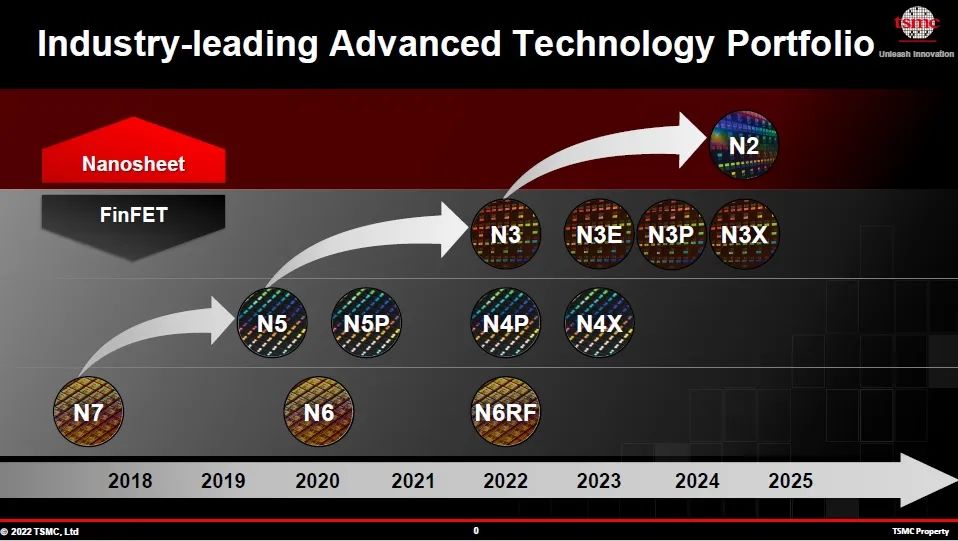

2018 年,台积电向所有人提供了*进的逻辑技术 (N7)。

2020 年,台积电以基于 N5 EUV 的逻辑技术引领行业。

2021 年,台积电推出 N4P、N4X 和 N6RF。

2022 年,台积电将推出覆盖广泛垂直市场的*进的 N3 工艺节点。我认为 N3 也将在 5 年内打破流片记录。

最后但同样重要的是,台积电在 2022 年宣布了面向大众的下一代工艺技术 (N2)。

工艺技术回顾

除了进一步讨论的一些例外情况外,支撑技术路线图演示有些例行公事——这不是一件坏事,而是表明正在成功执行先前的路线图。

路线图更新被提出了两次,一次是作为技术议程的一部分,另一次是作为台积电平台解决方案重点的一部分。回想一下,台积电特别确定了四个“平台”,它们分别接受开发投资以优化工艺技术产品,当中包括:移动;高性能计算(HPC);汽车;和物联网(超低功耗)。下面的摘要合并了两个演示文稿。

N7/N6

到 2022 年底,超过 400 个 NTO,主要在智能手机和 CPU 市场

N6 提供从 N7 的透明迁移,支持 IP 重用

N6RF 将成为即将推出的 WiFi 7 产品的射频解决方案

有一个 N7HPC 变体(上图中未显示),在overdrive VDD 电平下提供约 10% 的性能提升

对于 N6,基于逻辑单元的模块可以在新库中重新实现,以进一步提高性能,实现主要的逻辑密度提高 (~18%)。

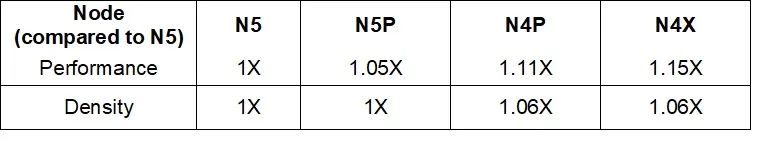

N5/N4

在生产的第 3 年,使用这个工艺的晶圆出货量超过 200 万片,到 2022 年底将达到 150 个 NTO

移动客户是*位的,其次是 HPC 产品

路线图包括正在进行的 N4制程增强

N4P 基础 IP 已准备就绪,接口 IP 在 2022 年第三季度可用(到 v1.0 PDK)

有一个 N5HPC 变体(上图中未显示,性能提升约 8%,HVM 将在 2H22)

N3 和 N3E

N3 将于 2022 年下半年开始进入 HVM

一年后大规模量产N3E 工艺变体;台积电期望该工艺在移动和 HPC 平台上得到广泛采用

N3E 已准备好开始设计(v0.9 PDK),在标准 256Mb 存储器阵列鉴定测试现场具有高良率

N3E 添加了“FinFLEX”方法选项,三个不同的单元库针对不同的 PPA 要求进行了优化

请注意,N3 和 N3E 与之前的台积电工艺路线图有些反常。N3E 不会提供从 N3 透明迁移的 IP。N3E 产品有点“修正”,因为采用了对 N3 的重大设计规则更改来提高良率。

台积电的早期采用者客户在积极的时间表上推动工艺 PPA 更新,无论是对现有基线(例如,N7 到 N6、N5 到 N4)的增量兼容变体,还是新节点。最初的 N3 流程定义具有良好的 NTO pipeline,但 N3E 将成为未来变体的基础。

N2

基于纳米片技术,目标生产日期:2025

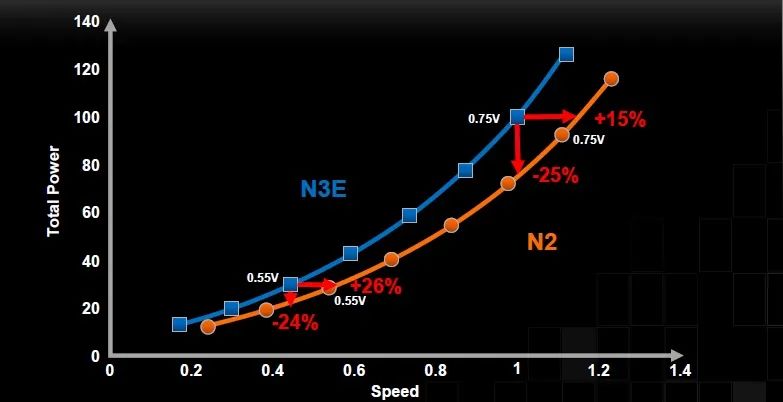

与 N3E 相比,N2 将提供约 10-15% 的性能提升(@iso-power,0.75V)或约 25-30% 的工号降低(@iso-perf,0.75V);另请注意上图中指定的工作范围低至 0.55V

N2 将为后端配电网络提供支持

顺便说一句,台积电面临两难境地,即不同平台的要求具有如此广泛的功耗、性能和面积/成本目标。如上所述,N3E 正在使用不同的库解决这些问题,并结合了定义单元高度的,不同数量的鳍。对于 N2 库设计,该设计决策被关于整个垂直堆叠纳米片数量的工艺技术决策所取代(器件纳米片宽度有一些允许的变化)。就纳米片拓扑而言,看看台积电选择为 N2 提供什么来覆盖移动和 HPC 市场将会很有趣。(下图来自台积电在 VLSI 2022 大会上的早期技术演示,描绘了 3 个纳米片。)

注意:有两种新兴的工艺技术正在被采用来降低功率传输阻抗和改善局部可布线性——即“埋地”电源轨 (BPR:buried power rail) 和“背面”配电 (BSPDN:backside power distribution)。对提供 BPR 的初步调查已迅速扩展到处理集成完整 BSPDN(如 N2)的路线图。然而,很容易混淆这两个首字母缩写词。

有关特殊工艺的分享

台积电将以下产品定义为“Specialty Technologies”(专业技术)类别:

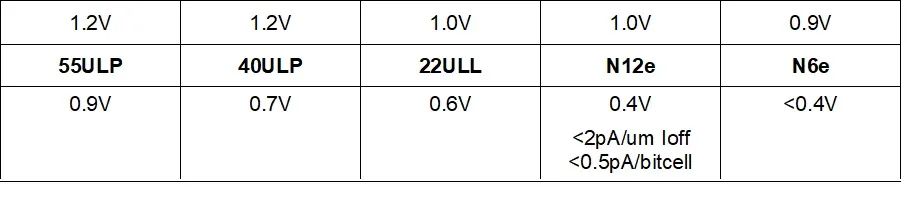

一、超低功耗/超低泄漏(使用超高 Vt 器件变体)

需要特别关注超低泄漏 SRAM 位单元设计

N12e 在生产中,N6e 在开发中(专注于极低 VDD 型号支持)

二、(嵌入式)非易失性存储器

1、通常与微控制器 (MCU) 集成,通常在 ULP/ULL 过程中

2、RRAM

需要 2 个额外的掩膜,嵌入 BEOL中(比 eFlash 的 12 个掩膜成本低得多)

10K 写入周期(耐久性规格),在 125C 时保持约 10 年

3、MRAM

22MRAM已经量产,重点是提高耐受度

2023 年量产面向Automotive Grade 1应用的 16MRAM

三、电源管理 IC (PMIC)

基于双极 CMOS-DMOS (BCD) 器件:40BCD+、22BCD+

适用于复杂的 48V/12V 电源域

需要极低的设备 R_on

四、高压应用(例如,显示驱动器,使用 N80HV 或 N55HV)

五、模拟/混合信号应用,需要独特的有源和无源结构(例如,使用 N22ULL和 N16FFC 的精密薄膜电阻器和低噪声器件)

六、MEMS(用于运动传感器、压力传感器)

七、CMOS 图像传感器(CIS)

N65 像素大小为 1.75um,N28 像素大小为 0.5um,过渡到 N12FFC

八、射频 (RF),从毫米波到更长波长的无线通信;即将推出的 WiFi7 标准被强调

“从 WiFi6 到 WiFi7 的过渡将需要显著增加面积和功率,以支持增加的带宽要求——例如,2.2X 面积和 2.1X 工号。台积电正在对 N6RF 产品进行认证,与 N16RF 相比,功耗降低了约 30-40%。这将允许当前使用 N16RF 的客户在开发 WiFi7 设计时大致维持现有的功率/面积目标。”

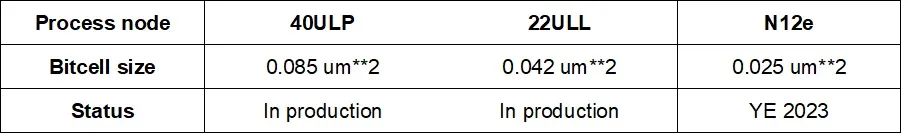

下图说明了这些专业技术如何成为平台产品(例如智能手机和汽车产品)的基本组成部分。还显示了用于这些应用程序的特征过程节点。

尽管智能手机开发的重点往往集中在主应用处理器上,但下表突出了对专业技术产品及其相关功能的极其多样化的要求。在汽车领域,向“区域控制”架构的过渡将需要一套新的汽车 IC。

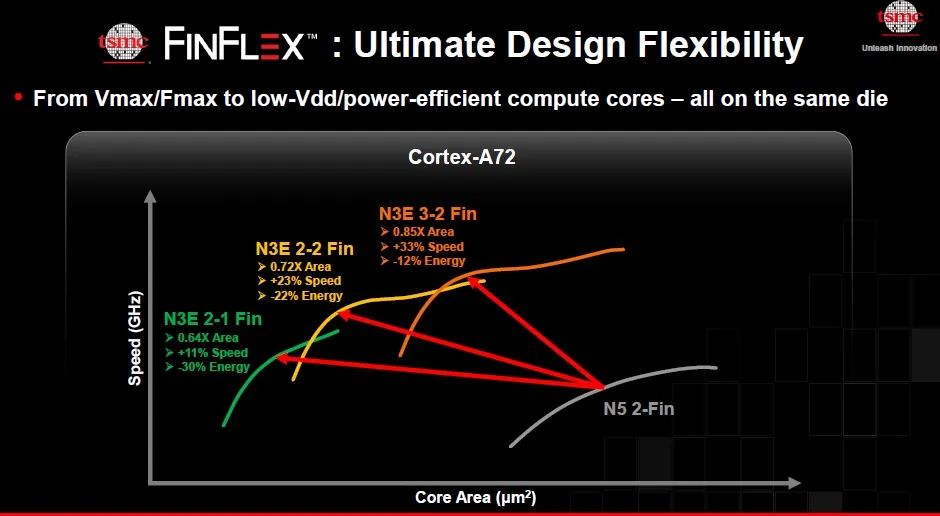

N3E 和 FinFLEX

台积电特别强调了新发布的 FinFLEX 方法,台积电表示,FinFLEX 将提供 N5 的全节点扩展。

随着 FinFET 技术节点的扩展(即从 N16 到 N10 到 N7 到 N5), fin profile和驱动电流每微米显著改善。标准单元库(Standard cell library)设计已发展为包含更少的 pFET 和 nFET 鳍,这些鳍定义了单元高度(根据水平金属布线轨道的数量指定)。如上图所示,N5 库使用 2-2 鳍定义——即 2 个 pFET 鳍和 2 个 nFET 鳍来定义单元高度。(N16/N12 使用 3-3 配置。)

N3E 的库定义面临几个问题。pFET 和 nFET 器件性能改进的规模并不相同。而且,就其 PPA(和成本)目标而言,移动和 HPC 平台应用程序的差异越来越大。移动产品专注于电路密度,以集成更多功能和/或降低功耗,同时对性能改进的要求不高。HPC 更专注于*化性能。

因此,N3E 将提供三个库,如上图所示:

2:1超低功耗库(轨道高度由 2 pFET:1 nFET 定义)

2:2高效库

3:2性能库

下图来自台积电的 FinFLEX 网站,说明了这个概念。

现在,在单个 SoC 上集成多个库并不是什么新鲜事。多年来,处理器公司开发了独特的“datapath”和“control logic”库产品,针对不同的目标:单元高度、电路性能、可布线性(即*单元面积利用率)和不同的逻辑产品(例如,宽 AND-用于数据路径多路复用的或门)。然而,使用多个库的 SoC 设计的物理实现依赖于每个设计块的一致库。

尽管上面的 TSMC 图片还描绘了每个块(block)一个库,但 FinFLEX 方法的独特性在于多个库和多个轨道高度将在一个块中混合。 将支持 2:1 加 2:2 库和 2:2 加 3:2 库组合。

台积电表示, “在一个块中启用不同的单元高度(在单独的行中)以优化 PPA。N3E 中的 FinFLEX 结合了新的设计规则、新的布局技术以及对 EDA 实施流程的重大更改。”

肯定会有更多关于 FinFLEX 和一般设计流程变化的信息。另一方面,需要有新的方法来:

一、floorplanning

为一个block规划两种不同行高的百分比组合

不同库行中单元的目标利用率百分比以实现可布线性(包括用于decap fill的 open cells)

对于具有显著百分比的低功率单元的块的 PDN“减少”方法

block的布局规划迭代次数(通过物理综合)以达到闭合

二、physical synthesis

合成将如何改善关键信号的时序

为了改善高负载信号的时序,综合通常会将库中的单元分配更新为下一个更高的驱动强度——例如,NAND2_1X 到 NAND2_2X。

对于 FinFLEX,第二个库提供了其他选项——例如,对 NAND2_1X_2:2 的更新是使用 NAND2_2X_2:2 还是 NAND2_1X_3:2。然而,如果选择后者,则需要将新单元“重新平衡”到块平面图中的不同行。这些选择的性能和输入/输出线负载的有效变化在物理综合期间难以估计(更不用说不同库单元的输出上升与下降的特定 RDLY 和 FDLY 延迟转换可能会不同地缩放)。

考虑到要使用的特定触发器单元(specific flop cells )时,单元选择选项变得更加复杂,不仅考虑到clock-to-Q 延迟的差异,还考虑到建立和保持时间特性以及输入时钟负载。寄存器中的各个触发器位在同一库中使用不同的驱动强度(并放置在本地)与将寄存器位重新平衡到对应于不同库选择的行相比,什么时候会更好?

三、子块级IP集成

块通常包含许多小的硬核 IP 宏,例如寄存器文件(通常由寄存器文件生成器提供)。由于跨越单个块的单元行高度不均匀,这些硬核 IP 宏将如何设计和放置?

四、物理设计期间的时序/功耗优化

与物理综合模块构建(physical synthesis block construction)选项类似,在物理设计流程的时序和功率优化步骤中,单元选择将面临困难的决定。例如,如果一个单元可以降低其分配的驱动强度以节省功耗,同时仍然满足时序,是否会考虑改变库选择,从而重新平衡行?单元格位置的变化会否定优化吗?

五、最后但最重要的是,启用 N3E FinFLEX 是否会产生新的 EDA 许可费用?

(几年前,我以前雇主的 CAD 部门经理在许可证成本加法器上大行其道,以实现多模式要求的布局和布线。鉴于支持 FinFLEX 所需的大量 EDA 投资,历史可能会重演,增加许可证功能成本.)

FinFLEX 方法无疑提供了一些有趣的选项。看看这种方法如何演变将非常有趣。

模拟设计迁移自动化

最后,台积电简要强调了他们在协助设计人员将模拟/混合信号电路和布局迁移到更新的工艺节点方面正在进行的工作。

具体来说,台积电定义了一组“模拟单元”,能够采用现有原理图、重新映射到新节点、评估电路优化和迁移布局,包括自动布局和(PG + 信号)布线。

N5/N4 和 N3E 的模拟单元库的定义已经完成,后续支持 N7/N6。TSMC 展示了一个通过迁移流程的运算跨导放大器 (OTA) 示例。

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。