早在十几年前,摩尔定律即将失效的消息就已经在业界闹得沸沸扬扬,一晃眼,十几年过去了,如今的芯片制程已经走到了3nm节点,并向着埃米时代迈进。看似一切都顺风顺水,但纵观整个发展史,你就会发现,风生水起的背后充斥着“欺骗”、“谎言”、“混战”、“挣扎”与“屈服”…

01

陷入风波的先进工艺

有关台积电和三星先进制程工艺“名不副实”的传言由来已久,原本随着先进工艺难度越来越大,相关话题的热度也开始逐渐下降,然而今年8月,TechInsights在Blog上发表的文章却再掀昔日浪潮。

TechInsights在对台积电和三星的4nm工艺进行剖析和拆解后,认为两家晶圆代工厂为了赢得彼此间的较量,因而放任客户声称他们采用了4nm工艺,实际上他们所谓的4nm工艺却仍是5nm技术。用5nm工艺假冒4nm,这件事情居然发生在了2022这个3nm量产年,不禁让人思考如今的3nm可还好?

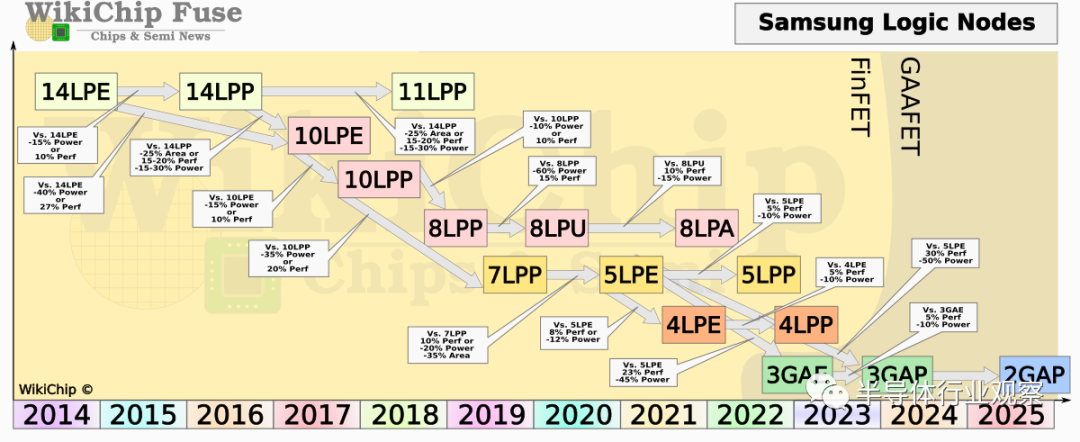

以已经宣布量产的三星3nm为例,三星官方消息显示,与三星5nm工艺相比,*代3nm工艺可以使功耗降低45%,性能提升23%,芯片面积减少16%;而未来第二代3nm工艺则使功耗降低50%,性能提升30%,芯片面积减少 35%。Wikichip根据官方数据粗略估计,*代3nm 3GAE的晶体管密度约为 150 MTr/mm²,而第二代3nm 3GAP的晶体管密度约为 195 MTr/mm²。需要注意的是,英特尔2017年发布的10nm工艺的晶体管密度就已经达到了100.8Mtr/mm2。

图源:Wikichip

Wikichip强调,由于从 FinFET 到 GAA 的过渡,因而降低高达 50% 的功率,如此大幅度的功率降低,对于三星代工来说,是自平面晶体管时代以来从未有过的。此外,就3nm性能而言,Wikichip也认为这些数字偏高,但仅略高于一些先前的节点。

台媒《经济日报》更是报道,分析师指出,三星的3nm制程所能达到的晶体管密度,最终可能与英特尔的制程4或者台积电的5nm家族当中的4nm相当,但是带宽与漏电控制表现会更好,带来更优异的效能。

那么台积电作为全球代工龙头,它的3nm就毫无争议吗?非也。

今年6月,台积电在2022 年技术研讨会透露了其即将推出的3nm节点的部分细节。但令人感到疑惑的是,技术研讨会上的大部分3nm消息都是关于 N3E ,也就是台积电第二代3nm工艺,而关于*代3nm的消息却寥寥无几。

到了今年8月,业内人士手机晶片达人在微博上爆料称,台积电内部决定放弃N3工艺,因为客户都不用,转2023下半年量产降本的N3E工艺,N3成本高,design的window又很critical,连苹果都放弃N3工艺。虽然台积电在论坛上辟谣了该说法,但最新消息显示,苹果A17芯片将有可能直接采用台积电*进的N3E工艺打造。

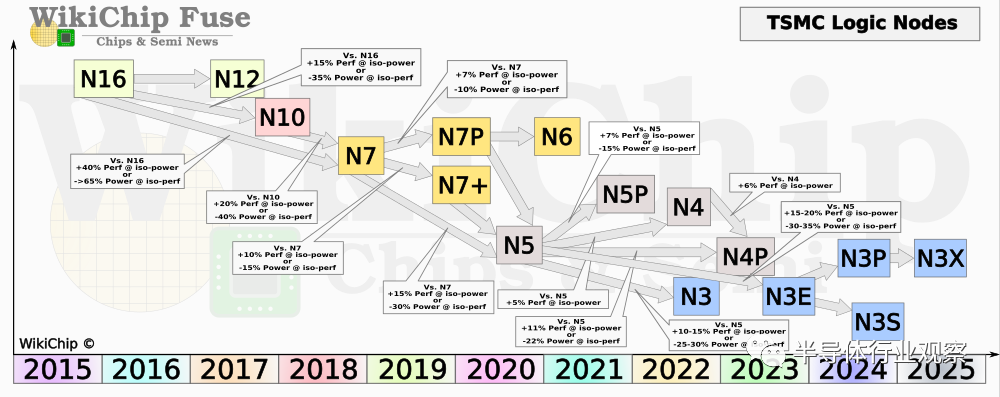

N3节点是台积电于2018-2019 年宣布,预计在今年下半年量产的*代3nm节点,与台积电的 Vanilla N5 节点相比,原始 N3 节点在 ISO 功率下可将速度提高约10-15%,数字逻辑的密度提高了约 1.7 倍,模拟逻辑的密度提高了约 1.1倍。鉴于台积电尚未公开任何设计规则,Wikichip粗略估计N3的晶体管密度范围约为 180-220 MTr/mm2。

虽然台积电方多次强调N3会在今年下半年量产,但是能否成为台积电3nm的主流工艺仍是一个疑问,关键之处就是在于N3E的出现。作为台积电第二代3nm工艺,N3E与N3有着极大的不同,消息显示两者之间的设计规则和IP 实现方式都有着较大的差异,这就意味着,客户没有直接的IP路径可让在N3上的设计迁移到 N3E。基于N3E,台积电还衍生出了N3P、N3X、N3S 和 N3RF四个变体,而N3似乎已经成为一个被人遗忘的存在。

图源:wikichip

倘若N3真的成为“弃子”,那么苹果等手机厂商则需要等到2023年下半年才能采用3nm处理器,更重要的是,据Wikichip估计,N3E的晶体管密度会略低于 N3 密度。无论是三星还是台积电,其3nm工艺的晶体管密度,似乎都与想象中有所偏差。

传统上,晶体管密度可以看作是芯片整体性能的指标,被业内奉为“圭臬”的摩尔定律指的就是芯片上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。从这个角度来看,当前3nm确实会令人产生一定的疑惑。

02

放弃“挣扎”的英特尔

其实,在迈入先进制程之后,晶体管密度问题就一直盘旋在芯片产业的上空。英特尔作为摩尔定律坚定不移的捍卫者,在2007年曾提出著名的“Tick-Tock(制程-新架构)”节点发展周期。按照英特尔的说法,Tick-Tock 的周期两年一循环,Tick 一年,Tock 一年。在Tick年,英特尔将会引入新的制程工艺;而在Tock年,英特尔将会使用上年更新过后的工艺推出采用全新架构的CPU。

按照Tick-Tock模式,英特尔工艺制程从65nm发展到22nm,但却在14nm卡了长达7年之久,Tick-Tock模式也在2016年被新战略PAO(Process-Architecture-Optimization 制程-架构-优化)替代。当英特尔还在困于14nm、10nm节点时,台积电和三星却已经从28nm/22nm,发展到16nm/14nm,并走到了7nm节点。

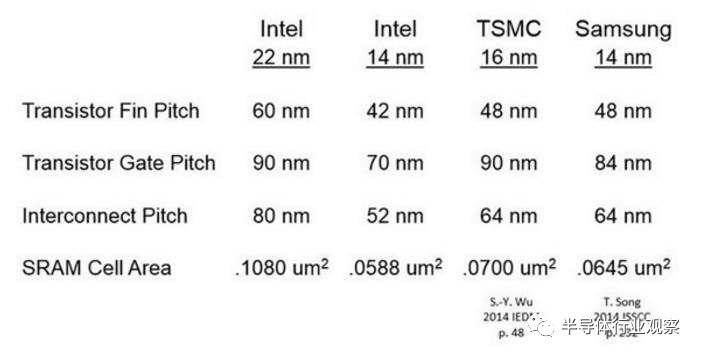

面对竞争对手在先进制程领域的大步迈进,英特尔对此表示不以为意。虽然英特尔14nm和10nm的升级周期都超过了两年,但是对应的晶体管密度也分别提升了2.5倍和2.7倍,符合摩尔定律的对于晶体管密度的线性增长要求。对比台积电、三星的16、14nm工艺,可以看出,英特尔的14nm工艺在这些关键指标要高于台积电和三星。

图源:电脑报

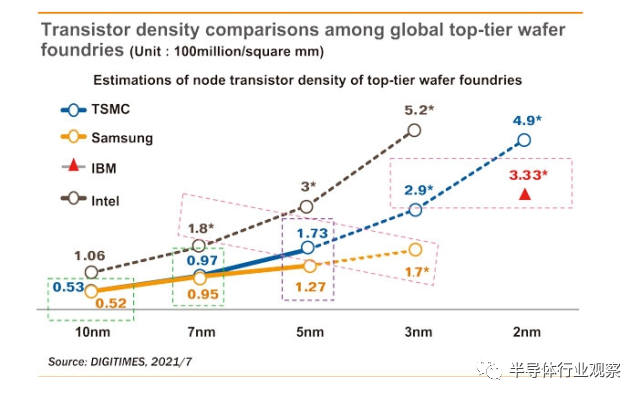

去年,Digitimes也对三家企业的芯片制造工艺做了对比,主要以晶体管密度作为参考指标,对比三家企业的10nm、7nm、5nm、3nm、2nm,其中Intel的5nm和3nm为预估值,台积电和三星的3nm、2nm工艺为预估值。

图源:Digitimes

Digitimes指出,在10nm工艺上,英特尔的晶体管密度就已*于三星和台积电,此后双方的差距在的差距逐渐拉大。就晶体管密度而言,台积电和三星的7nm工艺还稍微落后于英特尔的10nm工艺,到了5nm工艺上三星又与台积电拉开了差距,并且认为三星的3nm工艺才接近台积电的5nm工艺和英特尔的7nm工艺。

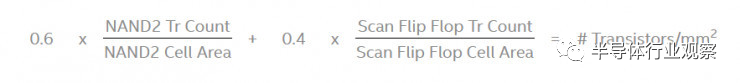

除了数据上的对比,2017年,当时的英特尔高级院士,处理器架构与集成部门主管Mark Bohr直接发布了一篇关于清理Intel工艺混乱命名的相关文章,直指业界在半导体工艺命名上的混乱状态,并给出了一个衡量半导体工艺水平的公式:

图源:英特尔

该公式主要分为两部分,一部分计算2bit NAND(4个晶体管)的密度,另一部分则是用来计算的是SFF(scan flip flop)的晶体管密度,0.6和0.4两个数字是这两部分的加权系数。Bohr表示衡量半导体工艺真正需要的是晶体管密度。

种种数据表明,如果从晶体管密度来看,英特尔的10nm/14nm的工艺制程在当时应该都属于拔头筹者,但竞争对手凭借命名优势一路高歌,反观英特尔却被冠上“牙膏厂”的称谓。

到了2021年,英特尔终究放弃挣扎,选择“同流合污”,更改了制程命名方式。英特尔未来5年技术路线图,对芯片的制程工艺进行了新的命名,10纳米Enhanced SuperFin更名为“Intel 7”、Intel 7纳米更名为“Intel 4”、其后是“Intel 3”、“Intel 20A”、“Intel 18A”。

随着英特尔的加入,如今的工艺制程命名似乎也已成定局。

03

命名“游戏”的开始

当前大家所熟知的XX nm工艺,指的其实是线宽,比如3nm意思就是栅极的最小线宽为3nm。而工艺的命名方式则遵循每个世代线宽缩减约 0.7 倍的规律,0.7x0.7约等于 0.5,也就是晶体管整体面积相比上一代缩小一倍,符合摩尔定律。

虽然XX nm工艺的命名方式在半导体业内已约定俗成,但其实早在1997年,也就是350nm之后,业界就已经意识到基于纳米的传统制程节点命名方法,不再与晶体管实际的栅极长度相对应。到了2012年,随着3D晶体管Finfet的出现,只用gate 的长度来衡量晶体管的特征尺寸已经远远不够了,还需要Fin的高度,Fin 的宽度,Fin Pitch,Gate length,Gate width等各种参数。

当下,0.7 倍的命名原则仍在继续,然而这些数据的实际意义却已经不大了,但台积电、三星等一众代工厂却从工艺命名上获得了巨大的利益和成功。

2014年,台积电利用其创新的双重曝刻技术,成为世界上*家开始批量生产20nm半导体的公司,并在同年创造了台积电最快的产能提升记录。凭借着20nm的优势,台积电从三星手中夺下了苹果的部分订单,台积电2014年第四季财报显示,合并营收约新台币2225.2亿元,与2013年同期相比营收增加52.6%,其中20nm制程出货占台积电第四季晶圆销售的21%。到了2016年,台积电已经取代三星,成为了苹果A系列处理器的*芯片代工厂。2016年台积电全年营收达到9479.38亿新台币,同比增长12.4%,造就了当时台积电历史上的最高纪录。

三星方面也是如此,在A8处理器以前,三星是苹果处理器的*代工厂,却在2014年失去了*地位,然而2015年凭借全球*14nm工艺制程实现反超,重新夺回了苹果处理器的代工业务。

众所周知,苹果A9处理器有两个版本,分别是三星的14nm和台积电的16nm,理论上讲,三星的14nm性能应该高于16nm,但从当时的消息来看,消费者的口碑就截然相反,三星代工的芯片在功耗和发热方面都不及台积电,这其实就已反映出工艺制成的命名原则已经背离了真实工艺性能。

即便如此,台积电和三星依旧“乐此不疲”,毕竟对于购买手机的消费者来说,绝大多数都是不会过于锱铢必较。以最新的Iphone 14来说,大家关注的大多在于只有Pro版本用上了最新A16仿生芯片,但对于A16与A15之间的性能差可能就一笑置之。

毫无疑问,商业上取得的红利是驱动命名“游戏”开始的关键点,但不可否认,台积电、三星和英特尔在整体半导体工艺的进展上也确实取得了巨大的进步,是推动整个芯片产业前进的强大引擎。

摩尔定律从提出到现在已经快60年了,随着时间的推移,我们不得不承认工艺制程的演进正在变得越来越困难,为了延续摩尔定律,台积电、三星、英特尔研发了各种先进技术,比如三星3nm中采用了GAA晶体管,台积电在先进封装领域的发力,英特尔的背面供电技术等…虽然当前芯片工艺进程或许有些受挫,但他们并没有放弃,相反正在积极研发各式各样的先进技术,希望有一天,会出现类似于“浸润式光刻”那样的颠覆性技术,能让制程发展实现大跨越。

从某种意义上来说,或许这些巨头延续原有的命名方式,也是他们表达捍卫摩尔定律的最后“倔强”。

04

写在最后

未来是未知的,但芯片产业向前发展是可以肯定的,我们相信未来先进制程一定会有更好的表现形式,但在下一个颠覆性技术出现之前,我们还需要台积电、三星、英特尔等巨头持续不断得创新,推出新技术…

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。