2022年12月,91岁的台积电创始人张忠谋站在亚利桑那州凤凰城的巨型工厂前,而台下是这个星球最有权势的半导体决策者们——苹果CEO库克、英伟达创始人黄仁勋、AMD董事长苏姿丰、美光CEO梅洛特拉、阿斯麦CEO维尼克。当然,还有年过80岁的美国总统拜登。

这里的每一个人单独拎出来,大概都可以给摩尔定律改上几个参数。但他们齐聚一堂,却是为了台积电3纳米的晶圆厂。2014年以后,美国本土*晶圆厂发展(主要是英特尔)一直掉队。而台积电则被认为将会是目前*的晶圆制造商,拥有*进的制程和*的良率。

众人开心,唯独张忠谋很忧伤。

他明白这大概是台湾地区半导体最高光的瞬间,却也是最黯然的时刻。他短暂回顾了台积电与美国的历史,然后喃喃吐出了一个名句,“全球化几乎已经死了,至少有那么一段时间,它们不会再回来。”

这句话像是说给自己听的,同样也像是说给台湾地区民众听的。

这场“大搬运”在台湾地区内部引发了一系列的负面反响,批评台积电“变节”,改名“美积电”的声音不绝于耳。因此,台积电相关人士被迫出来反复“澄清”,表示台积电依然会把*进的制程工艺留在岛内:

1纳米工艺确定落地新竹龙潭园区,总投资或将超320亿美元。

台湾民众听完心稍安了,有网友简单朴素地换算了一下:

∵ 1纳米等于3纳米的三分之一

∴ 台积电的能力是美积电能力的三倍

∴ 台积电依然是台湾的骄傲

但对于更多的人来说,1纳米制程本身就是一个令人疑惑的概念。

从微观极限的角度来看:硅原子的直径不到0.12nm,1纳米工艺意味着8.5个硅原子的大小。考虑我们的芯片工艺和算法能力谈不上“量子计算机”的水平,更解决不了在量子层面的种种反牛顿力学的工程问题,如此小的工艺足以让人吃惊了。

那么请问台积电生产的1纳米、3纳米、5纳米、10纳米工艺的芯片,到底是芯片上的哪一个部分呢?

答案是:无。

10纳米芯片的实际制程(最小金属间距)大约在40纳米左右;5纳米芯片的最小金属间距大约为30纳米;3纳米芯片的则大约为22纳米。

1纳米的芯片只存在于高校的实验室里,并且在短期内都不会出现在任何晶圆工厂中。

2019年台积电研发负责人、技术研究副总经理黄汉森在一次论坛中做出了这样的承认表态:“现在描述工艺水平的XX纳米说法已经不科学了……制程节点已经变成了一种营销游戏,与科技本身的特性没什么关系了。”

对于台积电来说,这是一场营销游戏;但对于消费者来说,这更像是一种共谋的“骗局”。

纳米制程:世纪乌龙

定名

要弄清楚黄汉森会这么说,我们还要回到芯片结构说起:

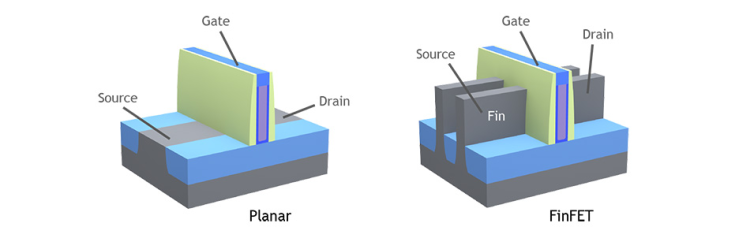

一个典型的晶体管其实分为三个单元,源级(Source-可理解为电流入口)、漏极(Drain-可理解为电流的出口)、栅极(Gate-可理解为开关-此概念将反复在文中出现)。栅极的开合,决定了电流是否通过,也就输出了所谓的0-1信号。

晶体管的“开关”实际上控制了0和1的信号输出,且栅极在很大程度上决定了这个晶体管的性能——栅极越短,晶体管开关的速度自然也就越快。

更重要的是,在早期晶体管的发展过程中,人们发现栅极的尺寸与晶体管密度的数据发展进程是高度吻合、呈现等比例缩放的。

于是在上个世纪70年代开始,人们便利用栅极的尺寸来命名制程的大小。

而以纳米来衡量制程,可以让大众更清楚地知道技术发展的进程。同时,行业也利用这个制程向公众传递一种“技术审美”:制程越小、代表芯片越先进。

一方面,摩尔定律规定芯片晶体管密度18个月要提升一倍、价格下降一半,这几乎只能通过降低制程来实现;另一方面,晶体管的快速增长会带来严重的功耗问题,也需要通过降低制程,来减少单个晶体管所需的电压。

否则,有人认为,如果沿着晶体管密度的线路发展,芯片的能耗密度将超过火箭发射器[10],实现真正的“为发烧而生”。

因此,单个晶体管的大小在当时成为了决定晶体管密度最重要的指标之一,在很大程度上可以决定晶体管的性能。

既然,晶体管大小决定了晶体管密度,而栅极又与晶体管大小高度相关。那么,用栅极大小来命名制程节点,似乎也没有什么问题。

但Bug却还是出在了对摩尔定律的崇拜上。

当时人们在用栅极来衡量芯片制程发展的同时,竟然还用摩尔定律“倒推”了一张栅极制程的迭代表格……

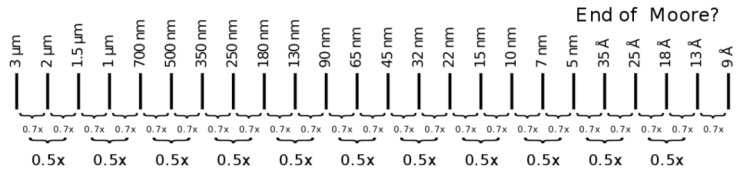

既然根据摩尔定律,芯片每一代的晶体管密度要提升一倍,那么对应晶体管的二维面积就要缩小一倍,那么一维长度大概就要缩减成上一代的0.7倍。

于是,一张基于摩尔定律的、乌托邦一般规整的制程节点表,就这么诞生了。

每一代制程都“准确地”比上一代缩小0.7倍,表格长度从3000纳米一直排到了0.9纳米……

图源:wikichip

这种“换算”的好处在于,它像一个天然的OKR——他将摩尔定律这个Objectives,落实成为了一个简单可量化的Key Results。在一定时间内,它也确实指引了芯片工艺的方向,似乎只要我们不断缩小制程长度,就能够到达摩尔给人类描绘的技术彼岸。

但这种过于理想化的技术想象,却客观上忽略了长期的技术变化。

最终历史证明,“栅极宽度与制程等比例变化”,“制程与晶体管密度等比例变化”,这两个最重要的同步性预测,其实只是上个世纪70-90年代的短暂产物。

破产

在90年代后,这种耦合就开始走向了破产。[1]

既然栅极是核心部件,那么随着芯片工艺的持续改进,厂商开始给栅极更多的优先级。他们采用更好的材料、甚至加高栅极的高度等等措施,来达到更窄的宽度,进而提升晶体管的响应速度[1]。栅极的缩小速度开始*于整体单元的缩小速度。于是,等式被打破了,制程节点开始失效了。

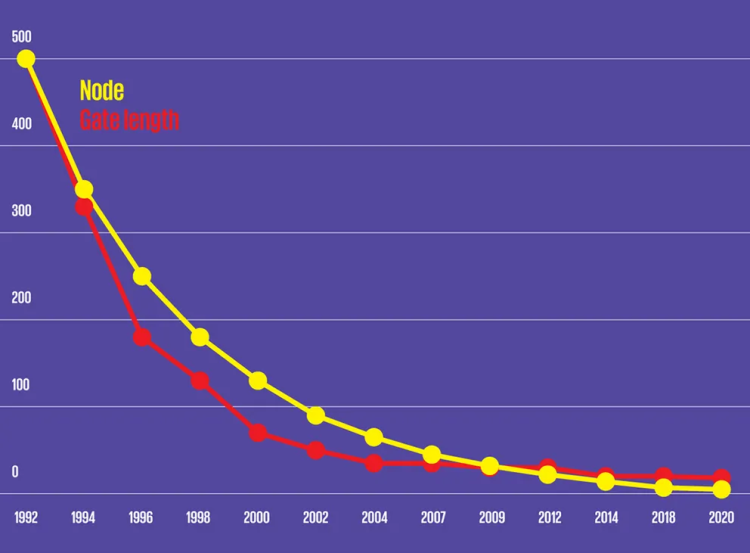

一开始,栅极的缩小自然*于制程节点:

在130纳米制程的时候,栅极的实际尺寸其实只有70纳米左右了,几乎*了纳米制程命名一倍左右。不过,既然栅极与单位整体不成比例,跳过阶段去命名芯片制程,多少就显得有点不讲武德、违背祖训了。再加之晶体管本身的发展速度还是大致沿袭了摩尔定律的预测,所以人们也还是沿用了此前的制程命名方式。

图源:ieee spectrum[1]

但人类不可能永远以几何级的速度去实现芯片制程的缩小,过薄的栅极会带来各种各样的工程学难题,比如“漏电”。制程变短带来的短沟道效应,会直接影响芯片的稳定性、功耗和寿命。于是,栅极制程的发展逐渐缓慢下来,与制程节点开始逐步靠拢。

这意味着人类必须重新思考芯片的设计架构,才能继续推动摩尔定律的历史进程。

如图所示,制程命名与栅级宽度的交叉点发生在2012年。

那一年英特尔彻底改变了传统的源级(Source)-栅级(Gate)-漏极(Drain)的平面结构(Planar),转而采用了下图右侧的FinFET鳍式场效应晶体管,通过加入鱼鳍Fin来帮助栅级提高性能。

这种结构的转变,也意味着芯片开始更多地从平面结构模式,转向3D、立体的设计思路[11]。当横向发展受挫的时候,晶圆厂开始比以往更多地向“天空”寻找空间。

图源:LamResearch

你甚至可以说,在22纳米以前的芯片原本就是“低垂的果实”。而如今,在材料物理学上没有飞跃的情况下,每一次向更低制程的“拱卒”,都需要耗费工程师头上更多的头发。

好消息是,摩尔定律还在苟延残喘;坏消息是,设计驱动似乎会变得越来越密集。

Planar结构用了二十多年,从3000纳米一直用到22纳米;FinFET结构用了10年,从22纳米一直到3纳米。此后,FinFET结构就逐步无法继续提供足够好的静电控制了,又需要在结构上进一步更新[3]。

GAA(全环绕栅级)被认为是下一代的技术路线。

例如在“3纳米”工艺上,三星就官宣了其全新的结构方案:MBCFET(多桥通道场效应晶体管multi-bridge-channel field-effect transistor)。而台积电方面预计会在“2纳米”工程中导入新的GAA结构方案[4]。

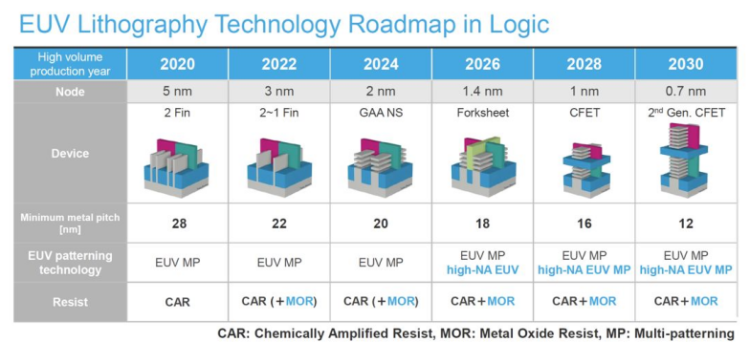

而GAA也不会是历史的终点。东京电子此前的一份报告中,就直观地展现出了其对芯片结构变化的可能性。GAA可能只会主导几代芯片,更强悍的制造工艺将会是CFET(Complementary FET,互补场效应晶体管),利用3D堆叠器件进行芯片制造,或许将主导“1纳米”以下的制程开发[12]。

图源:东京电子

从结构图来看,新的3D工艺就像是在平面上盖楼,来维持摩尔定律的增长。这将是一座宏伟的宫殿,栅级再不可能有曾经的参照系地位。实际上,以台积电和三星的制程数据为例,其10纳米芯片的栅级宽度大致在66-68纳米;3纳米芯片,大致在40-45纳米。

如上图所示,研究机构也转而使用了金属半截距作为参照。在3纳米之后的每一次技术迭代,晶体管半截距大概就只能进步2纳米左右。但命名系统依然遵照了摩尔定律的命名方式,以0.7倍几何级速度,头也不回地一代代迭代下去。

于是我们就出现了一个悖论:

晶圆厂在做一项夸张的人类雕刻活动,而这种复杂的结构恰恰是因为人类无法很好地驾驭原子层面的工艺,所以需要另辟蹊径才能满足摩尔定律。但摩尔定律的制程表,却还在不断强调极短制程的重要性。

摩尔定律在嘲讽摩尔定律。

在5纳米时期,制程差异大约是5.6倍;而到了7埃米时,制程差异大约会到17倍。

异化

严格来说,从90年代开始,以纳米命名制程节点的方式已经破产了30年了。从5纳米到3纳米,就像iPhone13到14一样,仅仅只是用于技术代际区分的营销意义,没有任何实指的工程学意义。

如果一定要牵扯上什么关系的话,那也只能是:

这颗芯片的性能相当于,假如我们能在Planar结构中造出0.8纳米制程的芯片、且没有微观量子找麻烦的情况下,该有的性能。

这大概要等到上帝把宇宙的代码开源以后了。

从理论上来说,目前这种制程节点命名的合法性来源其实只有一个:每一代晶体管数量翻倍。但即便如此,杀红了眼的晶圆厂也不会就此罢手。

人们渐渐发现,不同晶体厂对于“翻倍”的标准竟然也是不同的。

以14纳米向10纳米的过渡为例,英特尔与三星、台积电就出现了定名路线的争议。英特尔为了遵守摩尔定律规则,坚持将随后的两代芯片连续命名14+与14++,就此得名“牙膏厂”的雅称。而三星和台积电则直接将产品命名为10纳米,迎合了C端消费市场的换代审美。

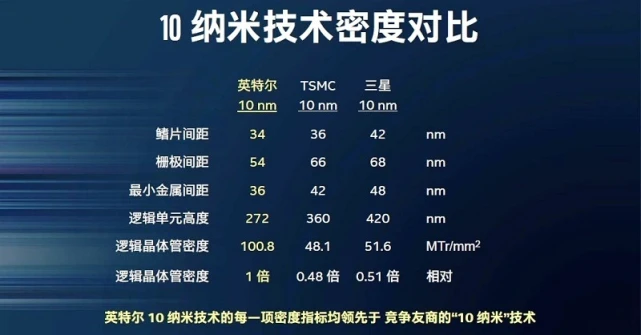

但当时两个阵营的芯片能力差距尚没有代际级的差距,于是就出现了芯片历史上有趣的一幕:

同样制程名字下,英特尔似乎比同类*了一代;但台积电与三星下一代来临的速度,似乎*了英特尔不止一代。

当时有不少媒体和机构都指出,如果按照台积电和三星的标准,英特尔14纳米+产品线其实可以被称作12纳米。而英特尔随后推出的10纳米芯片,其表现甚至部分优于台积电7纳米。英特尔也在媒体沟通会上,拿出了大大的10纳米制程的参数对比表格,暗示友商不讲武德[5]。

但当英特尔完成10纳米量产的时候,台积电5纳米产线都已经在建设中了。

图源:同名不同姓,参数差了一代|图源:EDN China[5]

纳米制程推出的目的之一,其实是让不同的晶圆厂,都能够在同一个标准体系下定名。但“各说各话”的定名方式,又客观上解构了标准。

纳米节点命名从服务摩尔定律的“公式”,变成了服务晶圆厂自身节点规划的“术语”。

这种随意性可以体现在本文开头时,媒体对于1纳米、2纳米芯片的宣传上。台积电所说的1纳米芯片,在摩尔定律的表格上实指18埃米制程。但已经没有人真的在乎这套天马行空的制程命名方式了:

1.8纳米制程,干脆又被抹零成为了1纳米…

这种越来越具有误导性的营销话术,很容易导致普通民众对芯片制造能力的误解。

一方面,普通人很容易对人类本身的材料技术工艺得出过于乐观、超出实际的印象;另一方面,随着制程名字越来越夸张,普通人也很容易得出“芯片制程发展走到*”的悲观结论——毕竟如果哪一天制程命名方式已经接近原子大小了,难道我们要切开原子核来制造晶圆吗…

后摩尔时代

在过去二十年的时间里,人们无数次地讨论摩尔定律的死亡与延续。而这种讨论的本质,其潜台词都指向了对摩尔定律的理解上。

支持者认为,晶体管数量大致保持了翻倍的趋势,故摩尔定律依然生命力旺盛;而反对者认为,摩尔定律首先应该是一个成本公式,暗含着IT技术的普惠性。

极端一点说,如果我们在实验室里造出小批量的、极其昂贵、但晶体管密度极高的芯片(事实上已经存在于很多大学实验室里),这一定跟摩尔定律没有任何关系。

纳米制程节点、而非晶体管密度,在早期能够代表摩尔定律的发展,就隐含了对这种技术平衡性的追求。纳米命名模式与实际制程的分道扬镳,其实本身就标志乌托邦式的摩尔定律开始解体——这本身就是摩尔定律的宿命,天下没有不散的宴席,技术的发展不可能是一条直线。

但纳米节点却扮演了一种“遮羞布”式的角色,人们假装摩尔定律还存在,却事实性地绕过了摩尔定律[7]。

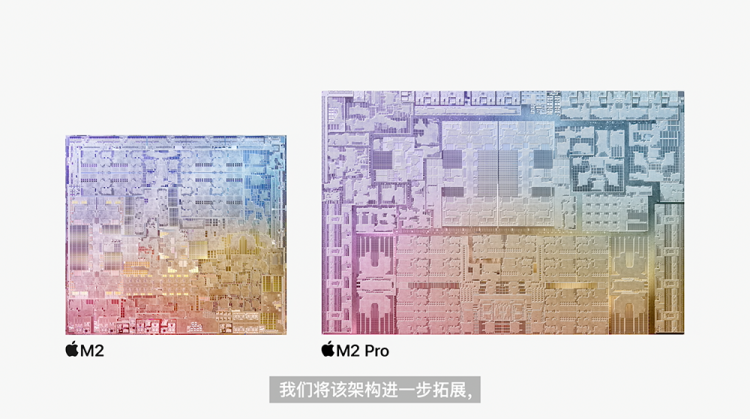

晶体管结构越做越复杂,核心越来越多,芯片大小越做越大。

图源:苹果

激进的进步姿态对环节各方都有着更高的要求:

于是我们发现芯片的控温越来越难了,明明是“5纳米”的芯片,却比“10纳米”烫得多;

我们渐渐发现旗舰芯片越来越贵了,对应终端设备的价格也水涨船高了;

有媒体援引机构调研数据表示,各个工艺下芯片开发成本正在着呈几何级的增长:

28nm工艺4280万美元→22nm工艺6300万美元→16nm工艺需要8960万美元。到了后期,芯片开发更是巨人的专场:7nm工艺2.486亿美元→5nm工艺4.487亿美元→3nm需要5.811亿美元→2nm工艺需要7.248亿美元[8]

而这仅仅是芯片公司的开发成本,对于晶圆代工厂来说,产线的建设投资成本更加高昂。

建设一座28nm晶圆厂投资额达60亿美元,但等到5nm晶圆厂投资额高达150亿美元,而兴建一条3nm产线成本为150亿~200亿美元[9]。而台积电最近宣布投资的“1纳米”工厂,投资规模高达320亿美元。

有传闻称,台积电3纳米芯片的报价将超过2万美元;5纳米时期的报价还只有1.6万美元,7纳米时不过1万美元。[13]

有多家海外科技媒体报道称,由于晶圆厂的报价实在过于昂贵,高通和联发科甚至不排除会弃用2纳米的芯片制程。

我们正处在一个“后摩尔时代”,进入一个全新的技术环境。

从这个角度来说,“纳米”则更像是这个时代的一个“史前传说”,它生动、古老、代表了美好时代的技术品德,但它却很难再回来了。

参考资料:

[1]《a better way to measure progress in semiconductors》,ieee spectrum

[2]《Introduction to Microelectronic Fabrication processes》,NPTEL

[3]《后FinFET时代的技术演进》,NicEda

[4]《台积电预测:2023年半导体市场将下滑4%》,中国电子报

[5]《全球首次亮相10nm工艺,英特尔如何玩转工艺节点的数字游戏》,EDN China

[6] Wikichip:3nm

[7]《只用一周时间,摩尔定律就死了一次又活了回来》,品玩

[8]《抢跑2nm,是否操之过急?》,半导体产业纵横

[9]《Industry watch: The expensive semiconductor game》,DIGITIMES ASIA

[10]《半导体制程,经历了哪些重大的发展节点?》,知乎周报-端点星

[11]《芯片中的“层”,层层全解析》,芯论语

[12]《后FinFET时代的继任者》,半导体产业纵横

[13]《14万一片晶圆!台积电3nm工艺报价翻倍:苹果成最坚定客户》,雷科技

【本文由投资界合作伙伴品玩授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。