从英特尔悄悄拿起,

到台积电发扬光大,

再被三星轻轻放下,

FinFET登台已10年之久,

如今随着摩尔定律逐渐失速,

新的时代迎来新的继承者。

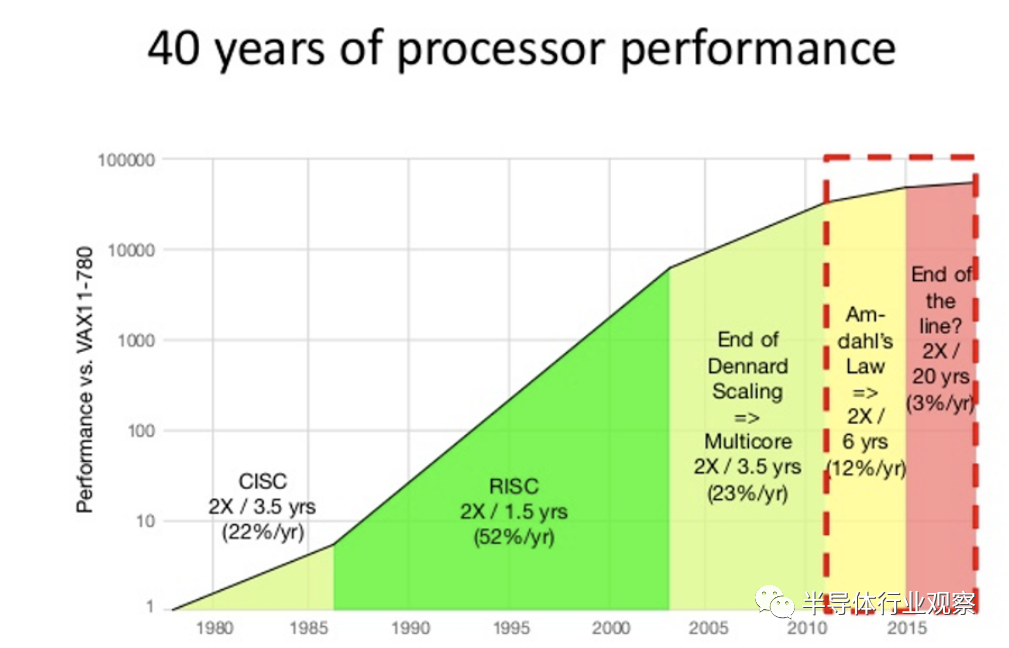

40年来处理器性能变化(图源:CAOS)

近日,据eenews消息,三星代工厂流片了基于环栅 (GAA) 晶体管架构的3nm芯片,通过使用纳米片(Nanosheet)制造出了MBCFET(多桥通道场效应管),可显著增强晶体管性能,主要取代FinFET晶体管技术。

该工艺需要一套不同于FinFET晶体管结构的设计和认证工具,因此三星使用了Synopsys的Fusion Design Platform。该工艺的物理设计套件(PDK)于2019年5月发布,并于去年通过了认证。伴随着此次成功流片,意味着三星3nm芯片大规模量产的时间点已正式临近。

三星执行副总裁兼代工销售和营销主管Charlie Bae表示:“基于GAA结构的下一代工艺节点(3nm)将使三星能够率先打开一个新的智能互联世界,同时加强我们的技术*地位”。

什么是GAA?

GAA——(Gate all around Field Effect Transistors,GAAFET),又称全环栅晶体管,是一种继续延续现有半导体技术路线的新兴技术,可进一步增强栅极控制能力,克服当前技术的物理缩放比例和性能限制。

据了解,GAAFET有两种结构,一种是使用纳米线(Nanowire)作为电子晶体管鳍片的常见GAAFET,另外一种则是以纳米片(Nanosheet)形式出现的较厚鳍片的多桥通道场效应管MBCFET,这两种方式都可以实现3nm,但取决于具体设计。从GAAFET到MBCFET,可以视为从二维到三维的跃进,能够改进电路控制,降低漏电率。

按照专家观点:GAA晶体管能够提供比FinFET更好的静电特性,可满足某些栅极宽度的需求。这主要体现在同等尺寸结构下,GAA沟道控制能力增强,给尺寸进一步微缩提供了可能;传统FinFET的沟道仅三面被栅极包围,而GAA以纳米线沟道设计为例,沟道的整个外轮廓都被栅极完全包裹住,意味着栅极对沟道的控制性能就更好。

Leti公司高级集成工程师Sylvain Barraud指出:“与FinFET相比,除了具有更好的栅极控制能力以外,GAA堆叠的纳米线还具有更高的有效沟道宽度,能够提供更高的性能。”

根据三星的说法,与7nm FinFET制造工艺相比,3nm GAA技术的逻辑面积效率提高了35%以上,功耗降低50%,逻辑面积减少45%。

能够看到,GAA晶体管结构标志着工艺技术进入了关键转折点,对于保持下一波超大规模创新所需的缩放轨迹至关重要。

三星和台积电的岔路口

目前,台积电、三星在5nm/7nm工艺段都采用FinFET结构,而在下一世代3nm工艺的晶体管结构选择上,两者出现分歧。

三星选择采用GAA结构。在今年的IEEE国际固态电路大会(ISSCC)上,三星首次公布了3nm制造技术的一些细节——3nm工艺中将使用类似全栅场效应晶体管(GAAFET)结构,率先开启了先进工艺在技术架构上的转型。

台积电则出于稳健考虑,选择在*代3nm工艺继续沿用FinFET技术,尽可能实现无缝过渡。毕竟在相同的制程技术与制造流程下,不用变动太多的生产工具,也能有较具优势的成本结构。尤其是对客户来说,在先进制程的开发里变更设计,无论是改变设计工具或者是验证和测试的流程,都会是庞大的时间和经济成本。台积电首席科学家黄汉森强调,做此选择是从客户的角度出发,采用成熟的FinFET结构产品性能显然会更加稳定,也有助于客户降低生产的成本。

不过,这或许只是一个短期策略。依托FinFET技术,台积电芯片工艺制程的终点来到了3nm,当鳍片(Fin)宽度达到5nm(等于3nm节点)时,FinFET将接近实际极限,再向下就会遇到瓶颈。

因此也有消息透露,台积电的2nm工艺将转向GAA架构(采用跟三星一样的MBCFET架构)。全新的MBCFET架构,以GAA制程为基础的架构,可以解决FinFET因为制程微缩而产生的电流控制漏电等物理极限问题。

综合来看,2nm或将是FinFET结构全面过渡到GAA结构的技术节点。在经历了Planar FET、FinFET后,晶体管结构将整体过渡到GAAFET结构上。

三星和台积电的选择考量都是商业决策下的结果。对台积电和客户来说,维持当前的设计体系,扩展FinFET似乎是一条更安全的途径。若最终的产品性能还能与竞争对手平起平坐,那台积电可能又将在3纳米产品世代再胜一筹。

对三星来讲,3nm时代在技术架构方面寻找差异化,试图进一步拉近与台积电芯片代工方面的技术差距。IBS首席执行官Jones表示:“与3nm FinFET相比,3nm环绕闸*有更低的阈值电压,并可能降低15%到20%的功耗,在某种程度上提供了更多的性能。”三星正在通过新的尝试和提前布局来寻求更多可能性。

FinFET走到了尽头?

过去十年,FinFET技术成功延续了摩尔定律,但时至今日,随着摩尔定律失速,FinFET也仿佛走到了尽头。

谈到FinFET,得从平面MOSFET开始说起,自平面MOSFET器件工艺诞生后,特征尺寸就随着摩尔定律的指引在不停地缩小。在晶体管特征尺寸微缩的过程中,虽然也遇到过各种困难,但是通过将铝互联改成铜互联,在栅极加入High-k材料、引入Stress engineering等方法都可以在不改变平面器件工艺的情况下把尺寸做小。

但是当栅极长度逼近20nm门槛时,对电流的控制能力急剧下降,漏电率也在升高,传统的平面MOSFET看似走到了尽头,材料的改变也无法解决问题。

对此,加州大学伯克利分校胡正明教授给出了新的设计方案,也就是FinFET晶体管,又称鳍式场效应晶体管。在FinFET中,沟道不再是二维的,而是三维的“鳍(Fin)”形状,而栅极则是三维围绕着“鳍”,这就大大增加了栅极对于沟道的控制能力,从而解决漏电问题。

胡正明教授2001年在学界正式提出FinFET方案,但真正被商业落实还是在十年以后。英特尔在FinFET工艺上率先出手,2011年推出了商业化的22nm FinFET工艺技术。随后包括台积电在内的全球各大半导体厂商积极跟进,陆续转进到FinFET工艺中。从16/14nm开始,FinFET成为了半导体器件的主流选择,成功地推动了从22nm到5nm等数代半导体工艺的发展,并将扩展到3纳米工艺节点。

FinFET工艺七大玩家进展(图源:芯思想)

FinFET工艺技术自2011年商业化后,体系结构持续进行改进,以提高性能并减小面积。到了5nm节点后,虽然使用了EUV光刻技术,但是基于FinFET结构进行芯片尺寸的缩小变得愈发困难。FinFET工艺制造、研发成本也越来越高,即使在7nm、5nm仍能坚持,但是再往前似乎已经是力不从心。

随着三星、英特尔两大晶圆代工巨头率先转向GAA工艺,正在预示着在更先进的节点上,FinFET将走向终结。根据国际器件和系统路线图(IRDS)的规划,在2021-2022年以后,FinFET结构将逐步被GAA结构所取代。

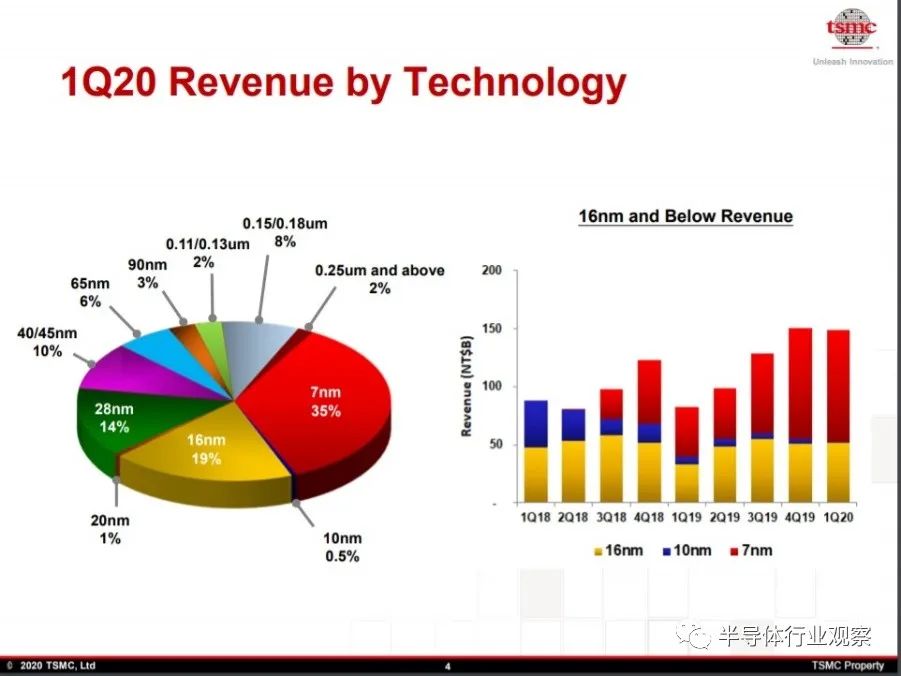

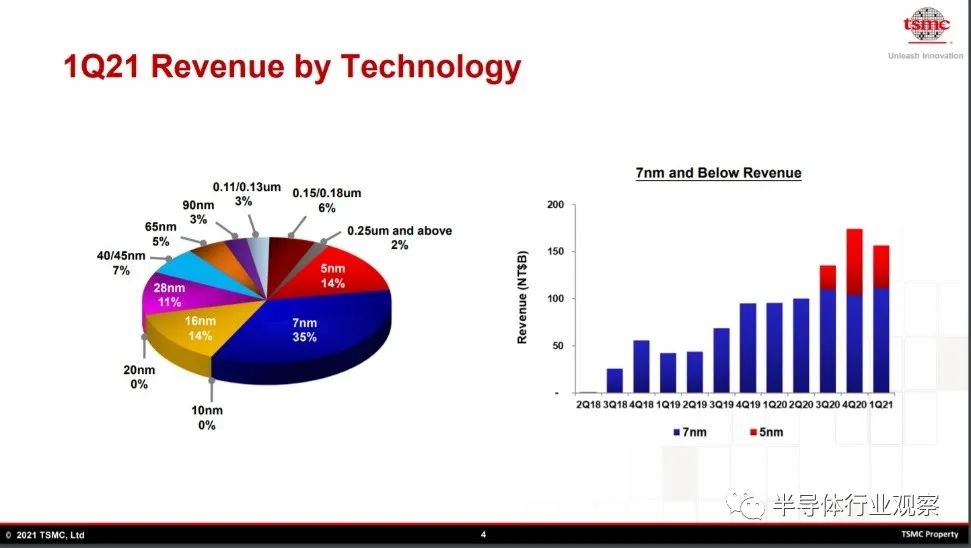

然而,虽然FinFET无法再继续深耕更先进的工艺节点,但在现有业务布局中仍占有相当份额,并正处于逐年增长的态势。这一点从台积电FinFET工艺收入中能够得到印证。

图源:TSMC

从上面数据可以看到,台积电2020年*季度FinFET工艺收入占比54.5%,在2021年*季度更是达到惊人的63%。FinFET收入增长背后,离不开台积电在此的专注和投入,在当前半导体短缺的情况下,台积电3年投资1000亿美元建设大量的FinFET产能,应对市场和客户需求。同时,台积电正在努力推动其500多个客户进入FinFET时代,加速其繁荣。

因此,现在说FinFET寿终正寝还为时尚早,台积电正在将FinFET带向多个领域。

芯片制造的未来走向

市场对于高性能芯片的渴望在不断推动技术的演进,在人们为3nm节点工艺担忧的时候,新的GAA技术出现了。那么除此之外,芯片制造未来还有哪些走向?

Forksheet FET & CFET

随着未来向更小制程的继续,将要求标准单元内nFET和pFET器件之间的间距更小。但是,对于FinFET和Nanosheet而言,工艺限制了这些n-to-p器件之间的间距。

除了Nanosheet,还有一些属于“全栅”类的其它技术选项。为了扩大这些器件的可微缩性,IMEC提出了一种创新的架构,称为Forksheet FET。

Forksheet可以理解为是Nanosheet的自然延伸,具有超出2nm技术节点的额外缩放和性能。Forksheet的nFET和pFET集成在同一结构中,由介电墙将nFET和pFET隔开。这个技术的优势就在于它有更紧密的n到p的间距,并减少面积缩放。与Nanosheet FET相比,在相同制程下,Forksheet FET的电路更加紧凑。

在从平面晶体管到FinFET再到Nanosheet的进化过程中,可以将Forksheet视为下一个发展路径。

此外,CFET——Complementary FETs(互补场效应晶体管)是2nm甚至以后另一种类型的技术选项。CFET由两个独立的Nanosheet FET(p型和n型)组成,是一种把p型纳米线叠在n型纳米线上的结构。通过这种叠加的形式,CFET等于是实现了一种折叠的概念,借此消除了n-to-p分离的瓶颈,能够将单元有源区域的面积减少2倍。

IBS首席执行官Handel Jones称:“CFET前景广阔,但目前还为时过早。向1nm CFET系列逻辑器件的发展推动了新BEOL和MOL解决方案的开发,但问题是即使增强了栅极结构,我们也需要增强MOL和BEOL,需要通过引入新的导体来补充这些集成方案,否则性能提升将受到限制。”

对于未来技术架构的演进趋势,IMEC认为:3纳米之前采用Nanosheet、2纳米采用Forksheet、1纳米采用CFET。在进一步的研究中,需要解决将这些器件完全投入生产的工艺挑战。

总而言之,目前这些仍在研发中的技术前景尚好,但也都有更自的挑战待突破,包含散热的控制和制造成本等,但可以看到的是,对于2纳米及之后的芯片制造,已有数项技术正在进行中,虽有困难但也是遥不可及。

Bizen晶体管架构

英国初创公司Search For The Next(SFN)和苏格兰芯片制造商Semefab合作开发了Bizen晶体管架构,可能从另一方向打破CMOS的极限。提出Bizen晶体管架构最初的目的就是为了创建具有较少掩膜步骤的芯片,使得同一块芯片上同时具有逻辑和功率晶体管,在这一初衷下创建一个LED驱动器的集成电路。

SFN首席执行官Summerland提出了使用齐纳二极管反向偏置特性的想法,该特性是由二极管N区域和P区域之间掺杂水平的突然变化产生的,最终致使量子电流的产生,以此来驱动双极晶体管。

具体而言,SFN的Bizen晶体管设计将双极结与齐纳二极管的概念结合在一起,利用量子隧穿效应从传统的双极晶体管中消除了电阻以及所有金属层。晶体管使用量子隧道连接栅极并能够建立多个栅极连接,这意味着可以在一个晶体管内创建多个非门和或门,从而缩小了逻辑电路的裸片。

半导体材料:铋(Bi)

从材料方面来看,目前硅基半导体主流制程已进展至5nm、甚至3nm的节点,芯片单位面积能容纳的电晶体数目,也将逼近硅的物理极限,芯片效能无法再逐年显著提升。

一直以来业界对二维材料寄予厚望,却苦于无法解决二维材料高电阻、及低电流等问题,前不久,由台大、台积电与麻省理工学院(MIT)共同发表的研究表示,由美国麻省理工团队发现在二维材料上搭配半金属铋(Bi)的电极,能大幅降低电阻并提高传输电流。随后台积电技术研究部门将铋(Bi)沉积制程进行优化,台大团队并运用氦离子束微影系统(Helium-ion beam lithography)将元件通道成功缩小至纳米尺寸,终于获得这项突破性的研究成果。

台大电机系暨光电所吴志毅教授进一步说明,使用铋(Bi)为接触电极的关键结构后,二维材料电晶体的效能不但与硅基半导体相当,又有潜力与目前主流的硅基制程技术相容,有助于未来突破摩尔定律的极限。

半导体设备:EUV的下一步

从DUV到EUV的过渡对延续摩尔定律起到了重要作用。为了继续微缩,几年前ASML开始研发下一代工具——High NA(高数值孔径)EUV,提升NA(numerical aperture,镜口率 )的基础上进一步提高半导体微细加工所需的电路分辨率。

ASML预计,High NA设备将在2025年或2026年进入商业生产。与传统的EUV光刻相比,High NA EUV光刻有望提供更先进的图案缩放解决方案。此外,在未来的工艺节点上,除了下一代EUV光刻技术外,新的沉积,蚀刻和检查/计量技术也在研究中。

写在最后

3nm即将发生,2nm也是如此。由于没有一种技术可以满足所有的应用,在芯片缩小和功能扩展的过程中,制程的进步、晶体管结构的变化和其他方法会交替进行,不断推动芯片性能向上攀升

在此情况下,除了制造商需要各显本事之外,如何从技术、市场与成本中取得*的利基,将是个企业间竞争的关键所在。特别是先进半导体制造的成本十分高昂,若不能在生产技术与制造成本中取得较佳的平衡,未来发展也将会非常艰辛。再考虑到半导体制造供应链庞大的牵连体系,不仅是制造设备,也包含设计工具和检验测试等部分,若没有优异的解决方案,也难以在竞争中保持优势地位。

在写下这篇文字的时候,前方又传来消息:“三星围绕3nm节点进行了大量营销和炒作,目前看起来形势严峻,产品性能似乎也进行了大量修改,基于GAA架构的3nm节点预计将推迟到2024年推出...”

但貌似也无伤大雅,2022年也好,2024年也罢。

不难预见,属于GAA晶体管的时代正在开启...

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。