昨日,韩国存储厂商SK海力士宣布,公司*代使用EUV光刻机生产的DRAM正式量产。

据介绍,公司旗下第四代 10 纳米級(1a)制程8Gigabit(Gb)LPDDR4 移动设备专用DRAM已经量产。作为SK海力士旗下*采用EUV生产的DRAM,与上一代产品相比,新产品可以将使相同尺寸晶圆生产的 DRAM 芯片数量增加 25%,并能将功耗降低20%。

在更早之前,三星已经率先量产了使用EUV光刻机生产的DRAM,在过去多年稍显保守的美光也宣布,将在2024年生产基于EUV的DRAM。至此,三大DRAM大厂都跨入了EUV时代。

DRAM面临的挑战

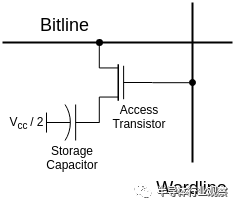

如下图所示,从原理层面上看,一个最简单的,存储一个 Bit 信息的 DRAM Storage Cell 的结构如下图所示。它主要是由存储电容(Storage Capacitor)、访问晶体管(Access Transistor)、字线(Wordline)以及位线(Bitline)四部分组成。

其中,存储电容通过存储在其中的电荷的多和少,或者说电容两端电压差的高和低,来表示逻辑上的 1 和 0;访问晶体管的导通和截止决定了允许或禁止对存储所存储的信息的读取和改写;字线决定了访问晶体管的导通或者截止;位线则是外界访问存储电容的*通道。

对于一种这样设计的器件,如何缩小其工艺尺寸,就成为了降低DRAM成本和尺寸的关键。

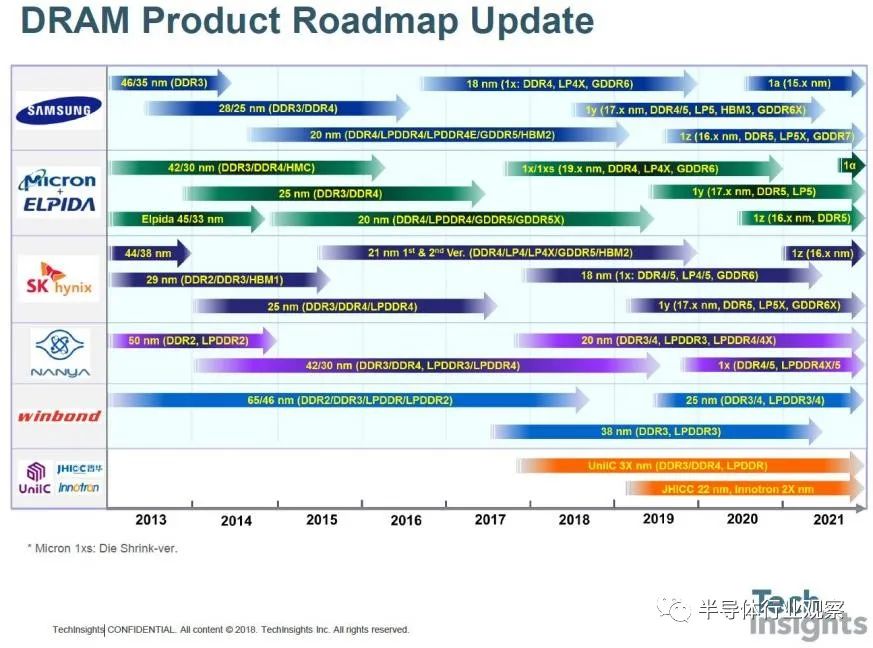

回看DRAM过去多年的发展,在历经了2008年的40nm级别(表示 49nm 至 40nm,4X4x)、2010 年的30nm 级别(39nm至30nm,或 3x)的推进。自2016年以来,DRAM就一直在10nm级别(19nm到10nm,或1X)徘徊,三大存储厂商(三星、SK海力士和美光)也都推出了多代的工艺。当中的每一次升级,都涉及在某些维度上减小 DRAM 单元尺寸,以实现增加密度和降低功耗的目的。

DRAM roadmap(source:IEDM 2018)

在后续的发展过程中,供应商在路线图上还提供了三代规模更大的 DRAM,分别是1anm、1bnm 和 1cnm。虽然供应商尚未透露这些部件的细节,但可以肯定的是它们仍处于 1xnm 节点。同时,我们也清楚认识到,DRAM的微缩面临新的挑战。

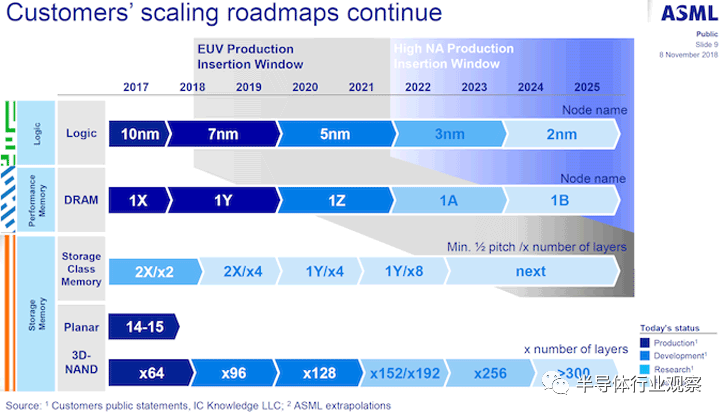

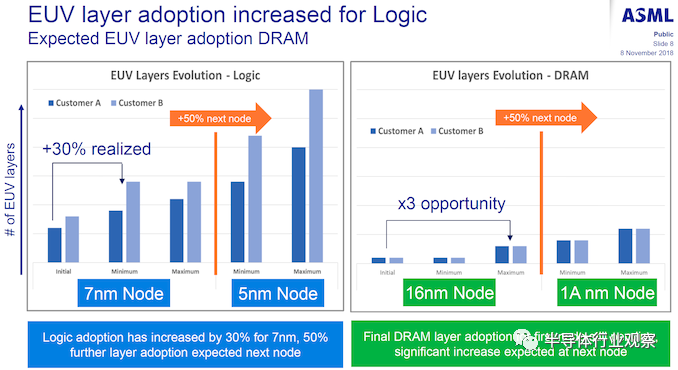

ASML对客户节点演进的预测

据了解,DRAM 的Cell尺寸使用nF²公式进行测量,其中 n 是一个常数,源自cell设计,通常介于 6 和 8 之间,F 是工艺技术的特征尺寸。因此,特征尺寸为 16nm 且 n=8 时,面积为 8 x (16 x 16) = 2,048 平方纳米。如果改用 14 纳米特征尺寸,面积为 1,568 平方纳米,减少 23%。这就是为什么缩小特征尺寸是值得的。因为通过这个方式,你可以在晶圆上获得更多 GB 的 DRAM。

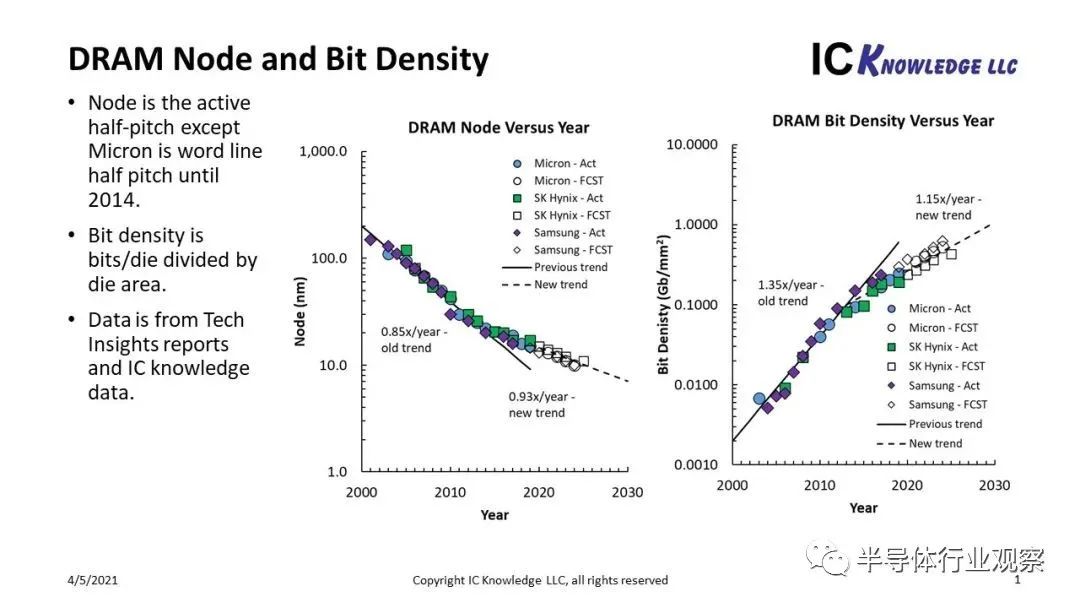

DRAM节点和位密度趋势

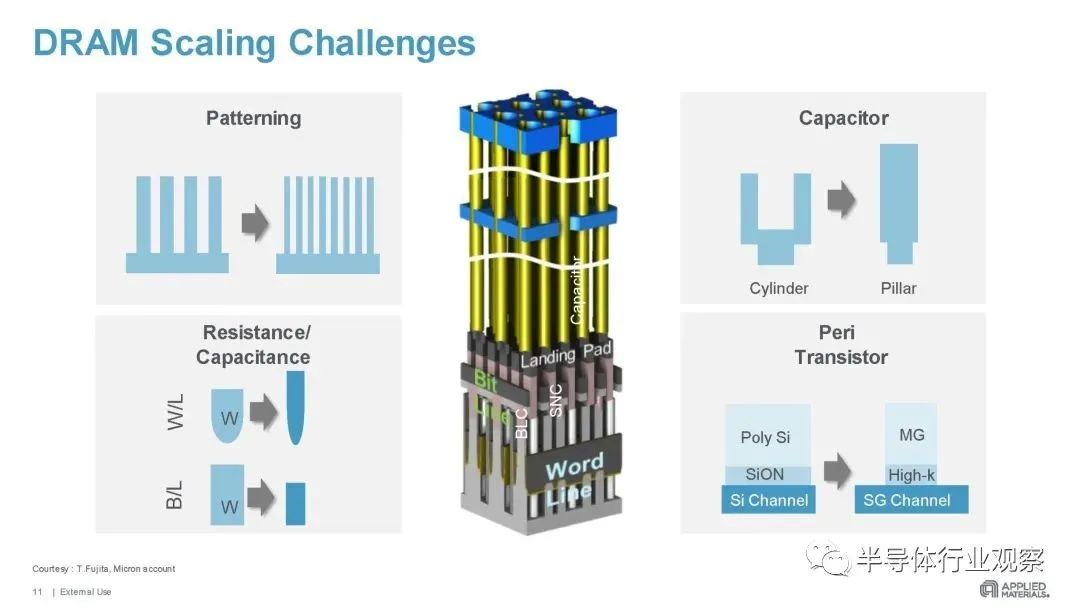

但正如应用材料的Regina在2021年2月举行的SPIE高级光刻会议上所说,DRAM的微缩正在放缓,为此需要新的解决方案来继续提高密度。按照他们介绍,DRAM的微缩迎来了多个方面挑战:分别是图案化(如何创建越来越密集的图案)、电容器(从圆柱体演变为柱状结构,需要对高深宽比进行构图)、电阻/电容(位线和字线需要提高电阻/电容才能提高访问速度)以及外围(Peri)晶体管(从含氧化硅的多晶硅栅到高K金属栅(HKMG)的演变)。

DRAM微缩面临的四大挑战

其中,涉及光刻机的电容器图案化最近已经通过XSADP( cross self-aligned double patterning)完成,但XSADP现在正在发展为甚至更复杂的XSAQP(cross self-aligned Quater patterning) 。如三星所公开的,另一种选择是间隔物辅助的图案化,该图案化可以使掩模上的孔密度增加3倍,但需要使孔尺寸相等的蚀刻。

为了实现以上目标,供应商在 1anm 及以后采用不同的路径。在这些节点上,特征更小,掩膜层更多。为简化流程,DRAM产业首次将EUV投入生产。

为什么是EUV?

所谓EUV,也就是Extreme ultraviolet lithography的简称。因为近几年的科技竞争,大家对这个使用在荷兰光刻机大厂ASML新型光刻机的技术并不陌生。得益于其波长特性以及先进的设计,EUV光刻机近年来被广泛应用到先进工艺逻辑芯片的生产中。

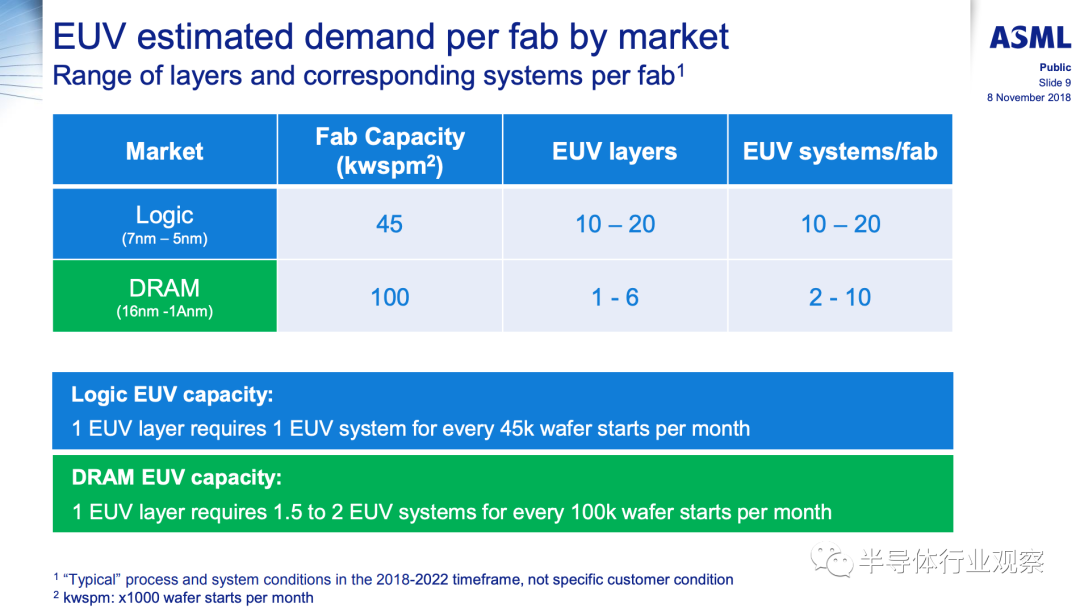

但其实根据ASML在2018年的规划,这也是一种会被存储领域采用的新技术。

ASML看好的EUV光刻机的机会

SK海力士方面表示,多年来,半导体光刻设备取得了许多进步,采用具有高数值孔径 (NA) 的大透镜或使用短波长光作为光源。然而,随着栅极长度减小到 30nm 以下,现有沉浸式 ArF 光刻设备的图案化能力达到了极限。

他们进一步指出,虽然对 18nm 以下的 DRAM 应用了多图案方法,但这会产生额外的处理阶段,并导致生产力损失和材料成本增加,所有这些都导致生产成本不断上升。由于处理步骤的数量接近 500 到 600 个,*的解决方案是通过应用更短波长的光,用“更薄的刷子”绘制微小的电路图案,EUV就是他们的的选择。

按照SK海力士的说法,半导体行业一直在准备以 EUV 光刻机实现 10 纳米级规模的工艺。通过利用 13.5nm 波长的光,EUV光刻机较之现有的 193nm 的 ArF 实现更精细的半导体电路图案,而无需进行多重图案化。借助这种方式,能将处理步骤的数量减少了,因此制造时间比当前的多重图案化技术(如四重图案化技术 (QPT))更短,从而使 EUV 成为迄今为止*的突破。

三星方面也表示,EUV能够帮助绘制更精细的电路,因此可以让芯片在相同的表面积内存储更多的数据。同时,使电路更精细意味着更多的逻辑门能够安装在单个芯片中。通过这样的方式,就可以让芯片变得更强大,更节能。在部署 EUV 后,芯片的表面积得到了更有效的利用,为此,业内的人争先恐后地为自己的生产线完善这项技术。

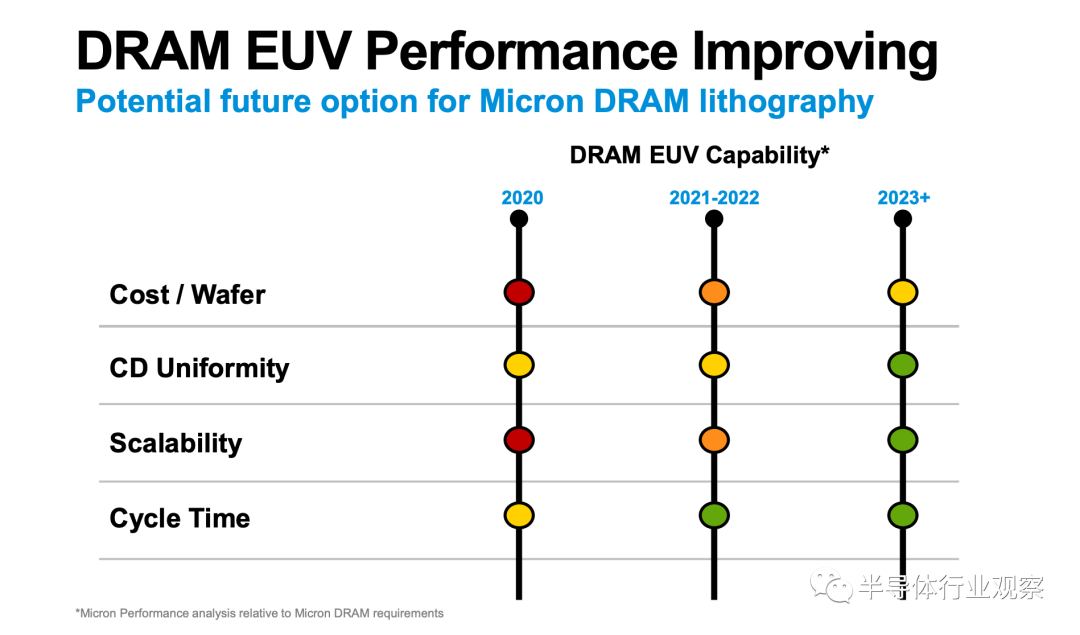

而从美光的介绍我们可以看到,如下图所示,在DRAM中引入EUV之后,能带来多方面的优势。

“使用 EUV,您可以获得更好的图案保真度。因为如果这些掩模层堆叠得越多,您获得的图像就越模糊。”VLSI Research 首席执行Dan Hutcheson表示。

三大厂商先后出招

在看到了EUV的机会后,三星、SK海力士和美光这三大DRAM大厂已经先后进入了EUV DRAM市场,或者至少已经公布了公司的EUV DRAM规划。其中,三星更是当中的先头兵。

在2020年三月,他们宣布推出了业界*基于 EUV 的10纳米级 (D1x) DDR4 DRAM 模块。三星方面表示, D1x 是一种实验性 EUVL 制造工艺,用于制造实验性 DDR4 DRAM,但不会进一步使用。

据三星当时的介绍,面向在今年推出的DDR5 和 LPDDR5,三星将使用其 D1a工艺,这是一种具有 EUV 层的高度先进的 14 纳米级工艺。与 D1x 技术相比,该技术有望使每个晶圆的生产率(DRAM 位输出)翻倍,这表明它使用更薄的几何结构。

三星方面进一步指出,EUVL 的使用将使三星(以及最终其他内存制造商)能够减少(或消除)多图案的使用,从而提高图案精度、性能和产量。后者将受益于高性能大容量 DDR5 芯片的生产,因为它们旨在提高性能(高达 DDR4-6400)和容量(高达 32 Gbps)。不过三星并为正式透露其 D1x 和 D1a 工艺技术使用了多少 EUV 层。

业内知名机构techinsights则在今年三月对三星电⼦量产的EUV DRAM芯片D1z 进行了拆解。据介绍,这个产品应该是在韩国平泽市(Pyeongtaek)的第⼆条⽣产线制造。

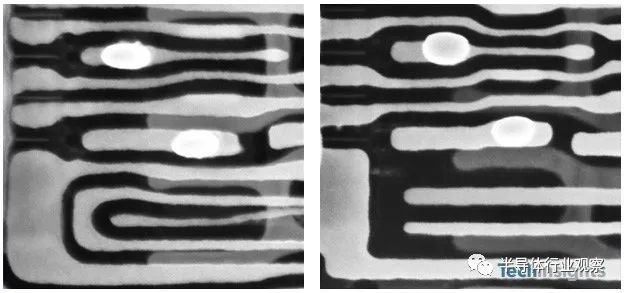

图1:比较三星的DRAM储存单元BLP图案:(a)是不采⽤EUV微影技术的版本

(b)是采⽤ EUV微影技术的版本。

techinsights在报告中进一步指出,在D1z 12Gb LPDDR5元件的制程整合上,三星电⼦只在⼀层光罩上采⽤EUV微影技术,单⼀SNLP (在记忆体单元阵列上)/BLP (在S/A感测放⼤器电路区)的临界尺⼨(CD/pitch)约40纳米,S/A区域的BLP线宽为13.5纳米。

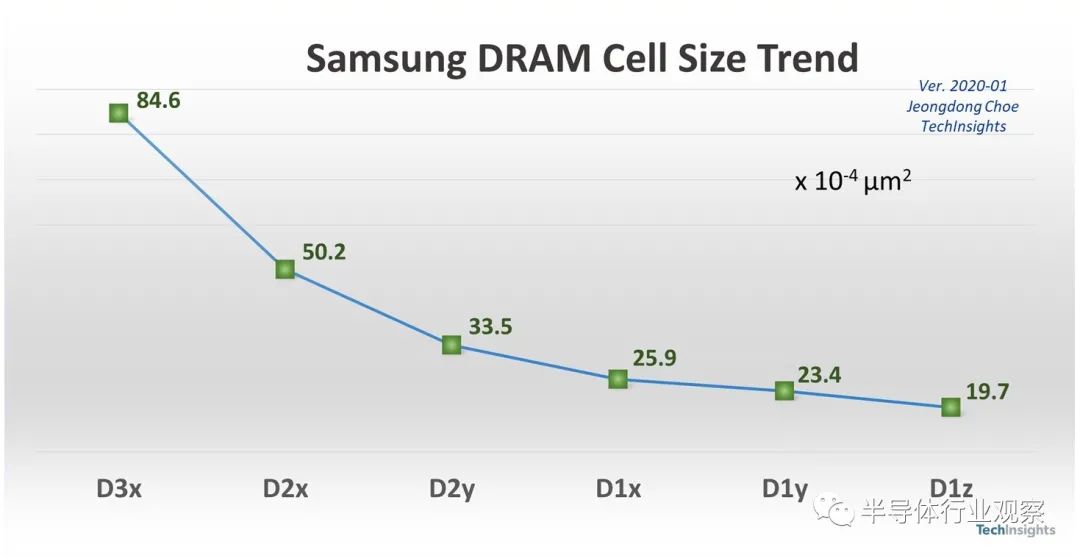

三星DRAM (从D3x到D1z)记忆体单元尺⼨变化趋势

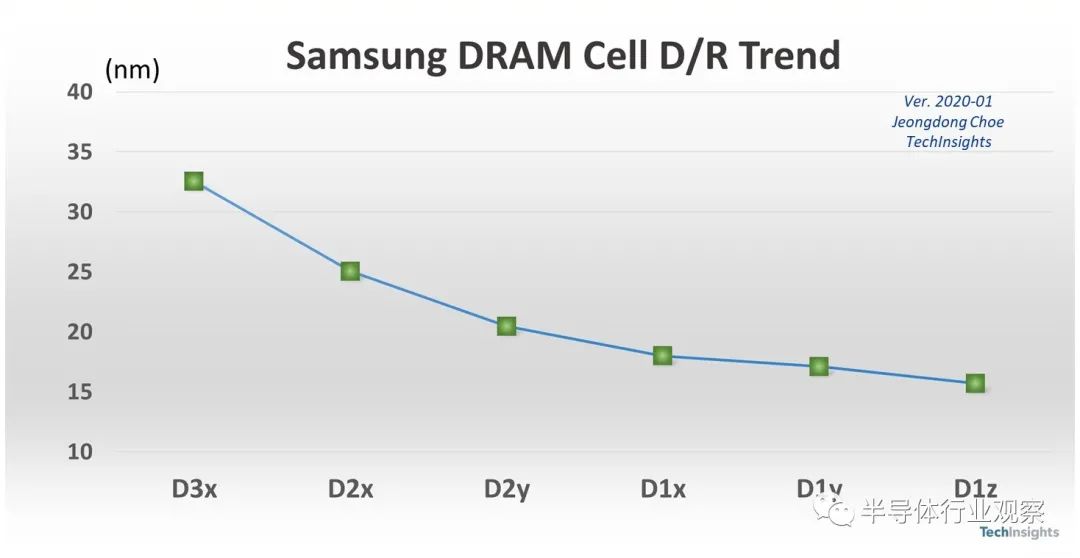

据报告。三星从D3x到D1z的DRAM记忆体单元尺⼨与D/R趋势变化分别如上图与下图所⽰。DRAM 记忆体单元与D/R微缩近年变得越来越艰难,但三星还是将D1z的D/R缩⼩到15.7奈米,比前⼀代D1y减少了8.2%。他们表示,三星将继续为下⼀代DRAM产品增加采⽤EUV微影的光罩层数,像是预计2021年量产的D1a与2022年量产的D1b。

三星DRAM (从D3x到D1z)设计规则变化趋势。

来到SK海力士方面,据报道,在去年五月,他们就开始了一个相当于15nm工艺的EUV DRAM研发。在今年二月,公司完成了其*条配备了用于 DRAM 芯片的极紫外光刻设备的生产线M16。如上文所说,公司将会首先在1a nm工艺上采用EUV工艺,未来,公司还会将 EUV 的实施扩展到 1b、1c 纳米线宽节点。从他们官方的介绍我们可以看到,SK海力士在DRAM中也会是只用到1层的EUV。而为了进一步保证EUV DRAM的供给,SK海力士在今年二月还与ASML达成了一个长达五年、总金额达到43亿美元的的EUV光刻机供应协议。

至于美光,在多次压榨DUV之后,并推出基于此的1a nm工艺之后。他们终于按捺不住,宣布了公司的EUV规划。

在六月底,美光表示,公司计划今年年底在其研究设施中安装 ASML 的新型 EUV 光刻设备 NXE:3600D。公司预计将把新设备应用于量产线进行实验,然后再正式投入量产。美光CEO表示:“根据我们对 EUV 取得的进展的评估,并与我们的技术战略和行业*的 DRAM 扩展路线图保持一致,我们计划从 2024 年开始将 EUV 插入到我们的 DRAM 路线图中。作为长期批量协议的一部分,美光已向ASML下达采购订单,以获取来自来他们的多个 EUV 工具”。

结语

虽然EUV能够给DRAM供应商带来不少好处,但正如应用材料的Regina所说,为DRAM实施EUV面临以下几个挑战:局部临界尺寸均匀性(Local Critical Dimension Uniformity:LCDU),因为这种变化会改变电气性能和蚀刻纵横比;孔尺寸– EUV对孔尺寸敏感,并且加工窗口狭窄;薄抗蚀剂– EUV抗蚀剂非常薄,需要硬化。

“EUV的一个主要问题是狭窄的工艺窗口;此外,当今的电容器间距极限大于40nm,这也是当前电容器图案化的EUV极限。将来将需要更小的间距,并且工艺可变性需要提高30%以上,才能实现缩放”,Regina进一步指出。

为此在他看来,EUV不足够解决DRAM的微缩问题,这需要我们在3至5年后,引入一种新的DRAM架构。当中涉及的一个有趣的选择是3D化,那就是将电容器从垂直结构变为堆叠的水平结构。

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。