在近期举行的EDA行业*会议DAC 2021中,芯片行业EDA巨头Synopsys和Cadence都分享了关于EDA行业未来发展的洞见,分别题为《Delivering Systemic Innovation to Power the Era of SysMoore》(驱动系统级创新以赋能系统摩尔定律时代)和《More Than Moore and Charting the Path Beyond 3nm》(3nm节点之后如何超越摩尔定律)。两篇行业分享都不约而同地提到了摩尔定律放慢以及EDA行业的下一个机会,其中的一些观点非常值得我们关注。

摩尔定律与EDA

在摩尔定律鼎盛之际,半导体芯片的集成度随着工艺节点的缩小每18个月翻一倍,同时也带来了大幅的性能提升。在那个时候,EDA工具必须能跟上工艺节点缩小的节奏,包括如何能够在集成电路规模指数级提升(18个月翻一倍)的情况下完成超大规模电路的逻辑和物理综合(布局布线等),以及如何能支持新工艺节点带来的新特性(例如晶体管建模,DRC规则等等)。总体而言,那个时候的EDA工具可以说是追踪摩尔定律的步伐,追随着工艺节点更新换代而增加对最新工艺节点的支持。

而随着摩尔定律接近物理极限,下一代工艺的进一步更新的节奏正在慢慢放缓,同时新工艺的成本越来越高但是对于性能的提升正在变小(只有15-30%左右),这使得使用成熟工艺的机会越来越多。另一方面,整个芯片行业对于性能、能效比等提升的追求并没有变慢,因此这就对于整体芯片的设计范式提出了新的要求,这同时也是EDA行业的机会。

首先,由于摩尔定律中新工艺节点带来的性能提升正在变小,因此芯片性能提升更多需要依靠设计,而不是仅仅依靠工艺改善。芯片设计中一个非常重要的环节就是逻辑综合和后端布局布线,因此在摩尔定律减缓的时代,事实上对于EDA工具的性能需求是提升了,因为芯片设计公司需要更强大更高效的EDA工具来充分挖掘半导体工艺的潜能,来实现芯片设计性能的提升。

其次,随着摩尔定律变缓,“More than Moore”正在成为新的设计范式,其中的一个重要改变就是使用高级封装和3D堆叠技术,将多个芯片使用封装的形式集成在一起,从而实现集成度和性能的提升。在这个角度上来说,芯片设计已经不仅仅是单个芯片的问题,而逐渐变为多芯片系统工程问题。因此,EDA工具也必须对这样的多芯片系统工程提供支持。

这两个机会也是Synopsys和Cadence在DAC 2021技术分享中的重点内容。针对这两个问题,Synopsys和Cadence不约而同地指出使用人工智能和对于高级封装技术的系统级芯片支持将是未来半导体EDA行业发展的主要方向。

EDA+人工智能

芯片EDA,尤其是逻辑综合以及布局布线等,往往从计算上来看是NP-hard问题,即在有限时间内几乎不可能获得全局*解,而大概率是得到一个性能还不错的次优解。使用经典算法通常会在电路规模提升时运行速度变慢,而且很多时候的最终结果质量很依赖于工程师人工给出的一些初始条件。总而言之,无论是运行时间、工程师资源还是最终结果的质量,EDA软件都存在瓶颈。

随着人工智能的发展,使用人工智能来帮助解决EDA工具中的NP-hard问题正在成为重要的方法。与AlphaGo解决围棋问题类似,人工智能也可以通过从海量数据中学习规律,来帮助EDA工具更快地获得更好的结果。理论上,人工智能同样没法确保能获得*解,但是可以帮助逻辑综合和布局布线算法更快地收敛到一个质量更高的解,从而能节省工具运行时间,节省工程师资源(对于工程师经验和人工干预的需求更低),并且提升最终结果的质量。

在本次DAC 2021上,Synopsys和Cadence都着重分享了关于人工智能在EDA工具中的应用。Synopsys的DSO.ai和Cadence的Cerebrus平台都能够在整个芯片设计流程中引入人工智能的帮助,从而加速EDA运行时间并提升质量(两家公司列举的例子中都提到了数倍的工程师资源和运行时间改善,同时在最终指标中则实现了10%以上的显著提升)。我们认为,这样的提升完全回答了在摩尔定律趋缓时代,EDA如何能帮助芯片公司更进一步挖掘半导体工艺的潜力并确保芯片性能提升速度不受摩尔定律的影响。此外,我们认为人工智能的引入也会对芯片设计方法论和行业带来改变,对于工程师的需求也会越来越减少,这从某种角度来说,也会进一步降低芯片设计的门槛,越来越多的系统公司将有机会能自研芯片,同时在芯片团队中,前端架构和微架构设计的重要性也会越来越高。

高级封装驱动系统性能提升

如果说人工智能的引入更多是提升EDA工具底层性能的提升,那么对高级封装的支持则将成为下一代EDA工具需要支持的最重要的新特性。

如前所述,使用高级封装后,EDA工具必须支持的设计对象不仅仅是一个芯片,而是多个芯片形成的系统。这个多芯片系统实际上给EDA带来了很大的挑战。例如,如何确保3D芯片堆叠时的芯片发热能满足散热的条件,如何确保不同芯片间的互联能满足信号完整性,当多个芯片形成系统时其工艺和电压的corner数也会大幅提升,如何确保时序设计能满足需求等等。换句话说,对于高级封装的支持是对于时序、信号完整性和热分析等传统EDA工具的一个升级,将传统仅仅用于二维单芯片的分析工具升级到对于2.5维和三维都能够支持。

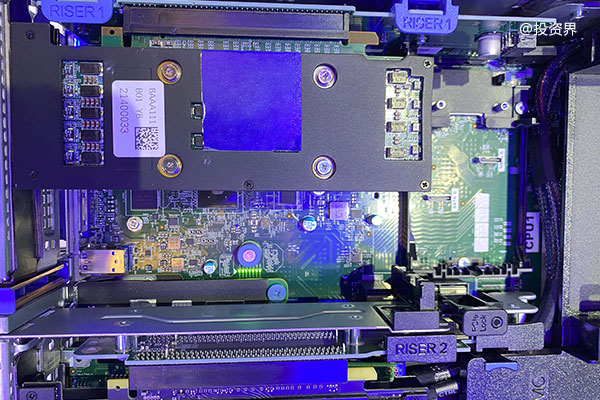

这同时也是Synopsys和Cadence在DAC 2021演讲中的另一个重点。Synopsys提出的解决方案名为3DIC Compiler,而Cadence的平台则是Integrity 3DIC Platform。两家公司提出的方案实际上都是给予他们之前已经相对成熟的时序、布局布线、信号完整性、热分析等EDA工具并实现针对高级封装领域的升级,从而能实现大幅降低流程运行时间,并提升分析结果质量,这样的升级也无疑是对于高级封装逐渐取代摩尔定律推动芯片性能提升的一个回应。

对中国EDA行业的启示

随着摩尔定律放缓,对于中国的EDA行业既是机会也是挑战。机会在于,如前所分析,整体芯片行业对于EDA的需求会变强,因此整个行业也会加强对于EDA的投入,对于中国EDA厂商来说,除了对设计和验证等传统技术上进行加强和查漏补缺以外,而人工智能等新算法范式则是一个新的起跑点,其中中国EDA公司和国际*公司都处于相似的起跑点上。而挑战则在于,由于芯片行业对于EDA的要求在提升,因此中国的EDA行业必须进一步加强自身的能力建设,才能更好地与国外巨头竞争。

我们认为,中国EDA行业应该首先把握住人工智能这一机会,因为整体来说中国的人工智能水准并不落后于其他国家,同时中国甚至在数据量等训练人工智能模型地重要资源上有一定优势,因此这也将成为中国EDA公司能实现追赶和超越的一个重要维度。而从另一个角度,高级封装对于时序、信号完整性和热分析地需求也在提醒中国的EDA公司一方面要加强这些基本工具地积累,同时也要积极地扩大自己支持的工具范围,因为对于高级封装来说最终一定是能将多种工具集成在一起的平台才能获得用户的青睐。如果能抓住这两个新的设计范式,中国的EDA行业必将获得大的进步。

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。