随着人工智能和元宇宙等对于高性能计算有强烈需求的应用逐渐成为半导体行业的新市场驱动,内存的性能发展也成了这些应用的重要支撑,这也成为内存行业继续大力投入新技术发展的重要动力。

在这些高性能计算系统中,内存带宽和容量将决定计算性能(例如人工智能算法中需要的大容量神经网络模型计算,以及元宇宙应用中的高性能渲染技术),这也就是高性能计算领域人们常常提及的“内存墙”。在许多高性能计算应用中,事实上逻辑计算并非整个系统的瓶颈,而数据存取才是整个系统速度的决定性因素。一方面,内存芯片技术需要进一步提升带宽和容量,而另一方面则需要在设计整体系统时,确保有高效的内存存取机制,从而打破内存墙的限制,进一步提升高性能计算的性能。

上周,三星召开了2022年技术发布会(Tech Day 2022),其中发布了三星在未来几年内的内存技术发展路线图。从中,我们认为其对于内存发展的主题围绕着“更快,更大,更智能”几个方向,这也与前面所讨论的高性能计算对于内存的需求相吻合。由于三星是内存芯片领域的*,我们认为它公布的路线图将会很大程度上反映整体内存芯片行业的发展动向。

更快:新内存接口将成为突破内存墙的主力

内存接口决定了整体系统可以以多快的速度存取内存里面的数据,因此也是决定了整体系统性能的重要因素。随着新一代内存接口的问世,高性能计算系统的性能也可望得到进一步提升。

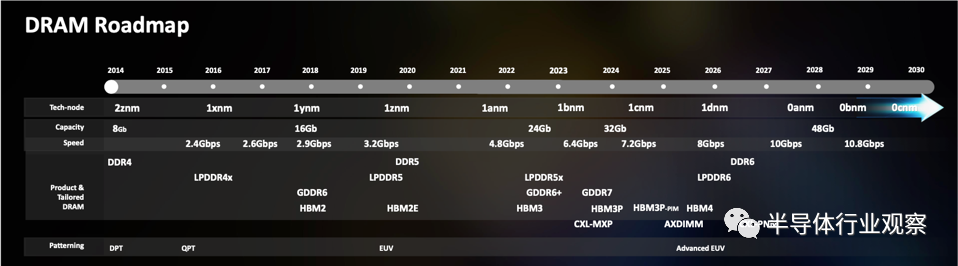

在三星公布的内存接口路线图中,我们可以看到涵盖不同领域的内存接口演进的速度。首先,在云端高性能服务器领域,HBM已经成为了高端GPU的标配,这也是三星在重点投资的领域之一。HBM的特点是使用高级封装技术,使用多层堆叠实现超高IO接口宽度,同时配合较高速的接口传输速率,从而实现高能效比的超高带宽。

在三星发布的路线图中,2022年HBM3技术已经量产,其单芯片接口宽度可达1024 bit,接口传输速率可达6.4 Gbps,相比上一代提升1.8倍,从而实现单芯片接口带宽819 GB/s,如果使用6层堆叠可以实现4.8 TB/s的总带宽。而在三星公布的路线图上,2024年预计将实现接口速度高达7.2 Gbps的HBM3p,从而将数据传输率相比这一代进一步提升10%,从而将堆叠的总带宽提升到5 TB/s以上。另外,这里的计算还没有考虑到高级封装技术带来的高多层堆叠和内存宽度提升,我们预计到时候单芯片和堆叠芯片到2024年HBM3p都将实现更多的总带宽提升。而这也将会成为人工智能应用的重要推动力,我们预计在2025年之后的新一代云端旗舰GPU中看到HBM3p的使用,从而进一步加强云端人工智能的算力。

除了HBM之外,在桌面和移动应用中,渲染也正在成为元宇宙相关应用的重要支柱。例如,在虚拟现实应用中,为了实现沉浸感,对于图像渲染的需求越来越强。高端虚拟现实设备会使用桌面级GPU做渲染,并且将渲染的图像通过串流传回虚拟现实设备中,而目前*的虚拟现实一体机则会需要使用移动级GPU在一体机中直接做图像渲染。这些应用都需要越来越大的显存带宽,而三星这次发布的GDDR7(针对桌面级应用)和LPDDR5X(针对移动级应用)都是针对这些应用的重要技术支柱。其中LPDDR5X的IO数据率可达8.5 Gbps,比之前LPDDR5(6.4 Gbps)提升30%,而GDDR7的IO速率可达36 Gbps,是之前GDDR6的两倍。

总体来说,这次三星从内存接口角度公布的路线图显示了从“更快”的角度,三星将进一步成为内存业界的领跑者之一,从而为半导体行业的进一步赋能人工智能和元宇宙等下一代应用提供支持。

更大:芯片和系统级创新将成为更大内存系统的关键

随着人工智能技术的演进,神经网络模型的参数也在越来越多(今年已经全面走向十亿级参数规模,未来几年预期将进一步实现数量级上的提升),而计算中需要使用的中间结果存储需求也对DRAM的容量提出新的需求。

为了满足这样对于存储容量的需求,我们同时需要芯片级和系统级的解决方案。在芯片层面,三星给出的答案是新一代使用1b(12 nm)特征尺寸生产的DRAM,从而实现更大的集成度。三星宣布1b DRAM将会在2023年量产,这也意味着三星在DRAM领域进一步巩固自己*的地位。

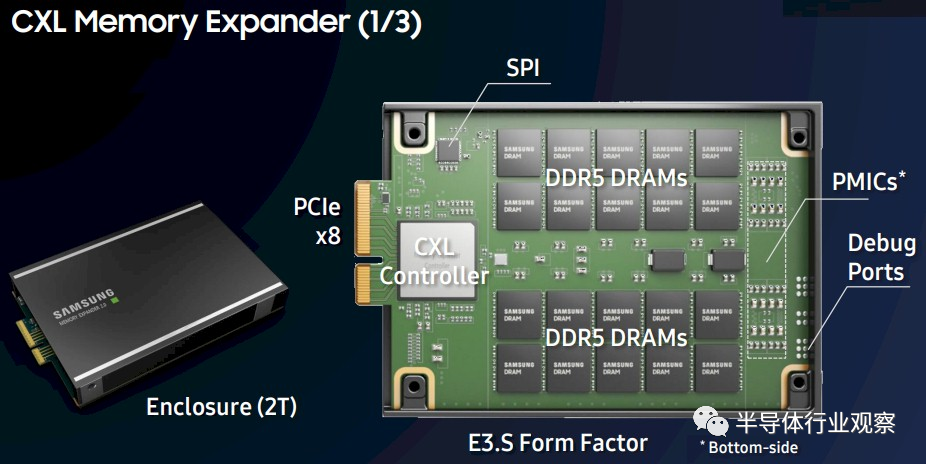

除了芯片级方案之外,系统级方案也是增加内存容量的重要方向。例如,在云端服务器市场,使用CXL技术做内存扩展就是一个很有潜力的方向。使用CXL做内存扩展的原理是把大量DRAM芯片集成在同一张内存扩展卡里,然后使用CXL主控芯片使用CXL协议接入高速接口中(PCIe),从而可以供系统直接使用,而无需占用DRAM插槽和接口,以起到内存容量扩展的作用。

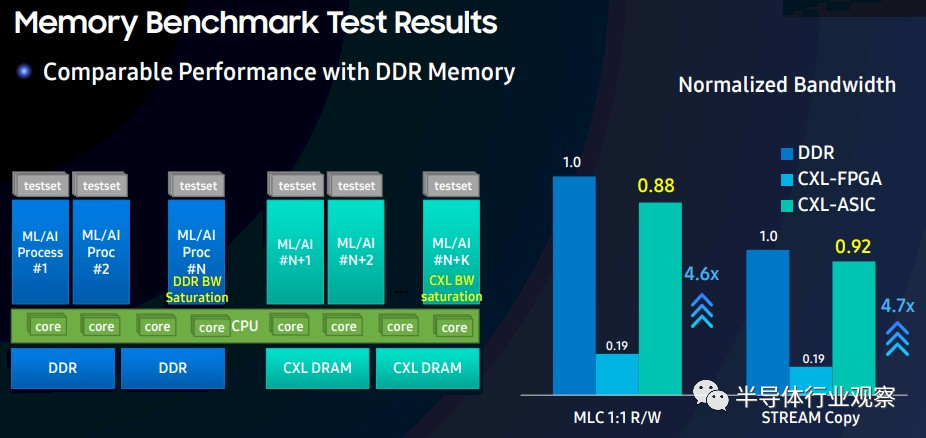

今年早些时候,三星公布了自己基于CXL内存扩展技术的最新结果,其中使用了为了CXL专门开发的ASIC主控芯片,并且在机器学习等重要应用中取得了和使用传统DDR内存接口几乎一样的性能,从而表明使用CXL做DRAM容量扩展从性能而言将是一个可行的技术方案,目前主要需要解决的是成本方面的考量,从而让该技术进一步得到应用。

三星这次也公布了自己在CXL领域的持续投资,未来我们预计将看到更多CXL内存扩展方面的产品。我们预计,CXL首先会在对于内存容量有巨大需求且对于性能有强烈需求的应用中(例如超大规模神经网络模型)开始得到使用,并且在未来越来越多地扩展到其他应用中去。

更智能:存内计算可望成为下一代内存新范式

除了在更大和更快两方面有提升之外,三星另一个布局方向是智能化DRAM,即针对机器学习和人工智能等应用使用存内计算和近内存计算这样的新技术。

三星主要的存内计算技术称为HBM-PIM,其中PIM即存内计算(process in memory)的缩写。其具体原理是在HBM内存中直接集成计算单元。传统的计算过程中,首先会从内存中读出数据,然后在其他芯片中的计算单元中做计算,然后把结果写回内存。而在HBM-PIM中,三星的技术路径是在给DRAM的指令不仅仅是读取和写入,也可以直接是计算,例如可以给“写入数据A同时将该数据和B相加”,这样在下次读出时,直接就得到已经计算过的数据,而无需再次读出并做计算。这样就节省了大量额外的数据移动开销,能实现更好的延迟和能效比。目前,三星已经在HBM2的DRAM中完成了*代HBM-PIM的开发(Aquabolt),而在三星公布的路线图中,我们也看到了HBM3-PIM列上了日程,预计在2024年完成开发。

除了存内计算之外,另一种技术方案是在DRAM旁边直接集成加速器逻辑以降低访问内存的开销,这样的技术三星称为AXDIMM(accelerator DIMM),在三星公布的路线图上预计2024-2025年完成开发。

我们认为,三星在智能化DRAM方面的布局从长远来看将会对内存技术和市场格局有深远影响,未来随着机器学习等应用对于内存访问提出进一步需求,我们认为这样的技术将有机会获得主流系统厂商越来越多的应用。

结语

随着人工智能等应用的演进,DRAM的未来发展也正在向赋能这类下一代应用的方向靠拢。从三星公布的路线图来看,未来的DRAM技术发展除了进一步提升DRAM芯片的容量和接口速度之外,还有在系统层面的革新方向(包括CXL内存扩展以及存内计算/近内存计算等智能化DRAM),DRAM技术的演进将会带给芯片和系统厂商越来越多的技术创新机会,而这些创新将会进一步推动新应用和新场景的出现,从而让整个领域进一步发展。

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。