领 先的晶圆代工厂和IDM厂商正朝着2纳米(或同等)技术节点的量产迈进,其中环栅(GAA)纳米片晶体管将发挥核心作用。GAA纳米片器件架构作为FinFET技术的后继者,旨在进一步缩小SRAM和逻辑标准单元的尺寸。

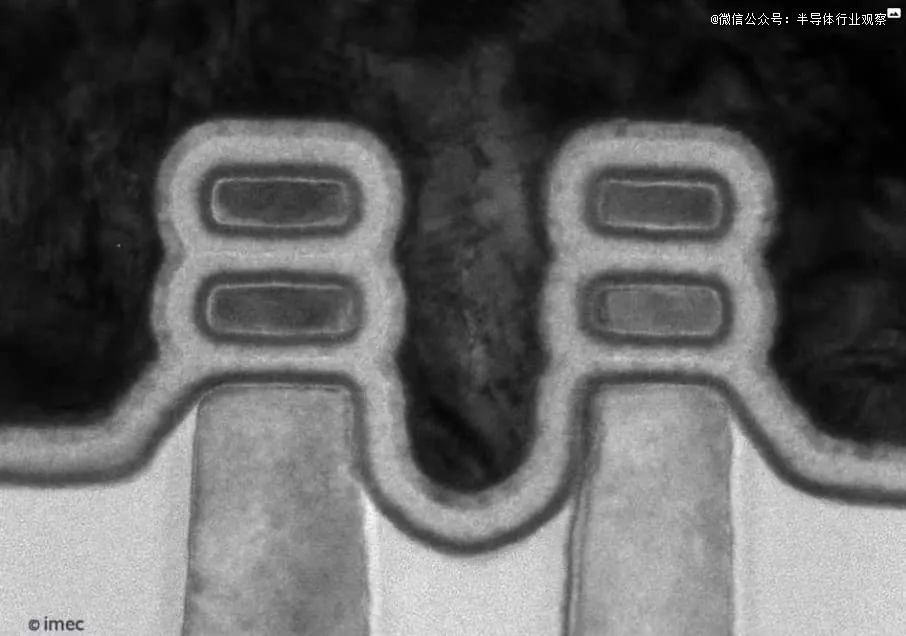

GAA 纳米片器件的主要特点是垂直堆叠两个或多个纳米片状导电沟道,每个逻辑标准单元包含一个堆叠用于 p 型器件,另一个堆叠用于 n 型器件。这种配置允许设计人员进一步缩小逻辑标准单元高度,其定义为每个单元的金属线(或轨道)数量乘以金属间距。设计人员还可以选择加宽沟道,以牺牲单元高度为代价换取更大的驱动电流。除了面积缩小之外,GAA 纳米片晶体管相比 FinFET 还具有另一个优势:栅极从各个方向包围导电通道,即使在较短的通道长度下也能增强栅极对通道的控制。

图 1 – GAA 纳米片器件的 TEM 图像

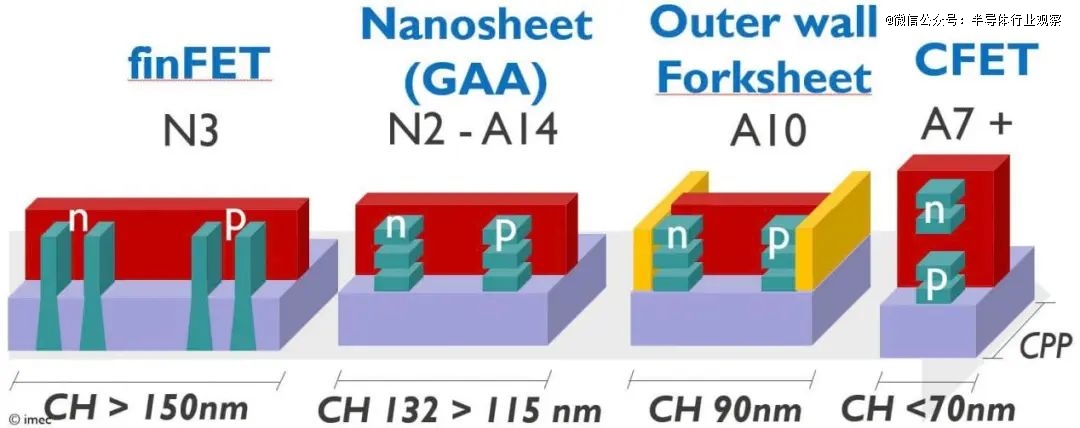

在芯片制造商过渡到CFET(complementary FET )技术之前, GAA 纳米片技术预计将持续至少三代技术。

由于其 nMOS-pMOS 垂直堆叠结构, CFET 的集成复杂度显著高于常规纳米片器件。根据 imec 的路线图,这使得CFET 的量产只有从A7 节点开始才可行。这意味着GAA 纳米片时代必须至少延伸到 A10 技术节点,预计该节点的单元高度将小至90 纳米。然而,在不影响性能的情况下缩小基于 GAA 纳米片的标准单元尺寸极 具挑战性。

这正是forksheet 设备架构可能带来缓解的地方,它是一种非破坏性技术,比常规 GAA 纳米片技术具有更大的扩展潜力。

01

Forksheet,1nm的依仗

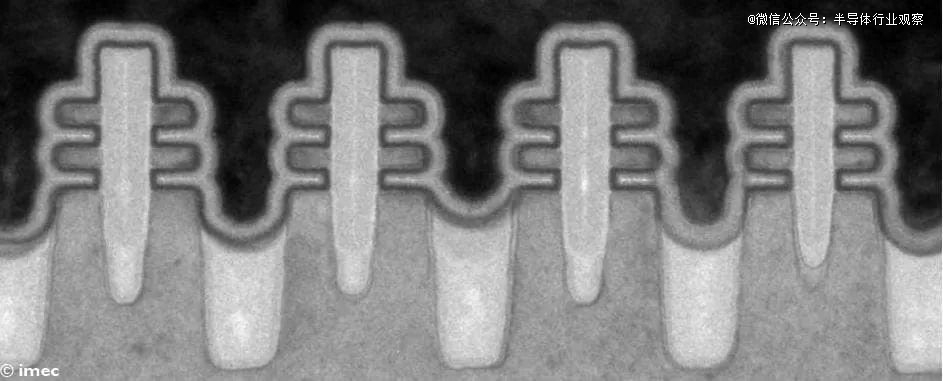

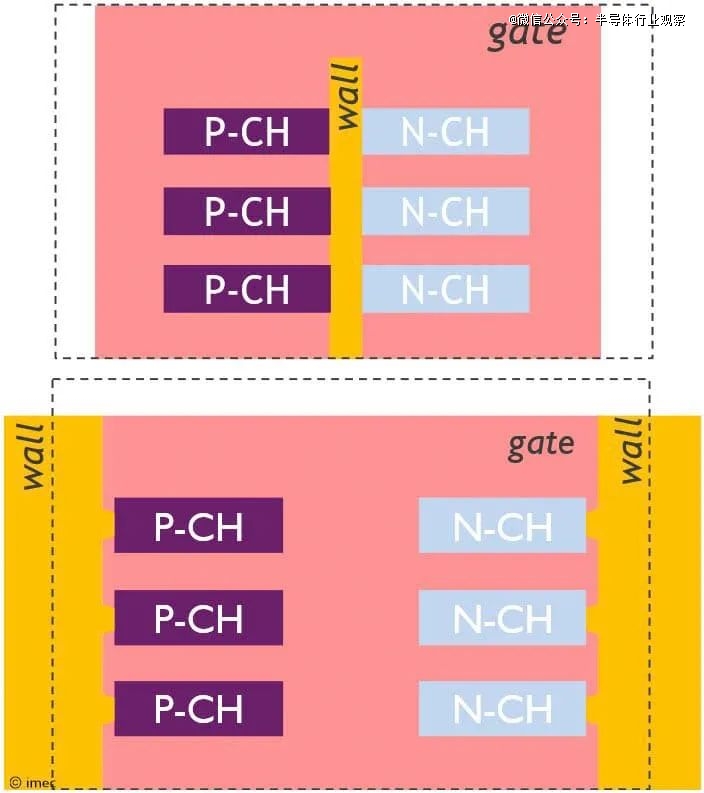

2017 年,imec 推出了 forksheet 器件架构,首先作为 SRAM 单元的缩放助推器( scaling booster),后来作为逻辑标准单元缩放推动器(scaling enabler)。其首次实现的独特之处在于在栅极图案化之前在 nMOS 和 pMOS 器件之间放置一层电介质壁(dielectric wall)。由于这堵墙位于逻辑标准单元的中间,因此该架构被称为“内壁”(inner wall)forksheet。该墙在物理上将 p 栅极沟槽与 n 栅极沟槽隔离,从而实现比 FinFET 或纳米片器件更紧密的 n 到 p 间距。这允许进一步缩小单元面积(单元高度高达 90nm),同时仍提供性能提升。

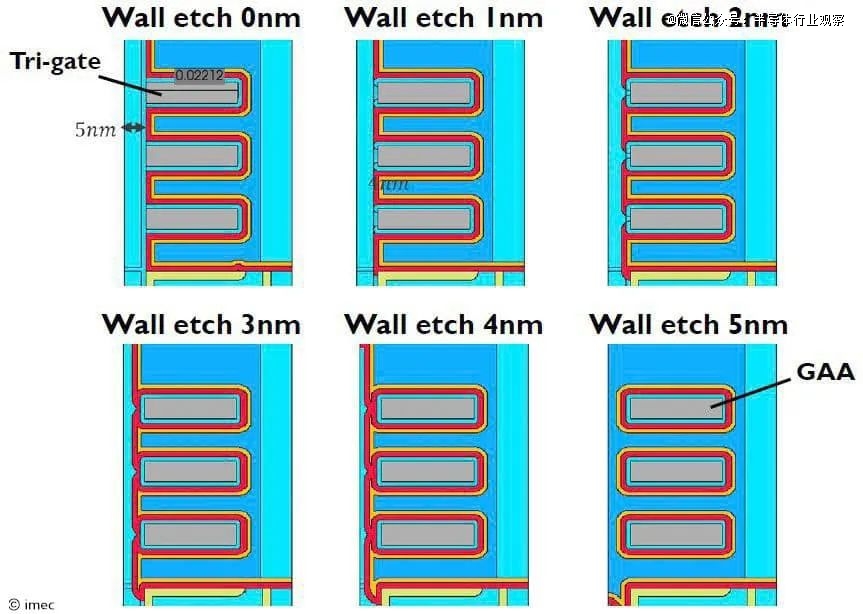

在这种“内壁”配置中,这些薄片由三栅极叉形结构(tri-gate forked structure)控制,该器件的名称由此而来。

图 2 – 内壁叉片装置的 TEM 图像

在 VLSI 2021 上,imec 展示了300 毫米内壁 forksheet 工艺流程的可制造性。对功能齐全的器件进行电气特性测试,证实 forksheet 是最有前景的器件架构,能够将逻辑和 SRAM 纳米片的微缩路线图扩展到A10 节点。由于集成流程重用了大部分纳米片的生产步骤,因此从纳米片到 forksheet 的技术演进可以视为非颠覆性的。

02

可制造性正受到挑战

尽管硬件演示成功,但对可制造性的一些担忧仍然存在,这使得 imec 重新考虑并改进其最初的 forksheet 设备架构。主要的挑战与内壁本身的可制造性有关。

为了实现 90nm 逻辑标准单元高度,介电壁需要非常薄,在 8-10nm 范围内。但是,由于在设备工艺流程的早期制造,壁面会暴露于所有后续的前端制程 (FEOL) 蚀刻步骤中,这些步骤可能会进一步减薄壁面,这对壁面材料的选择提出了相当高的要求。

此外,为了能够实现特定于 n 或 p 的工艺步骤(例如 p/n 源极/漏极外延),专用掩模必须精确地落在薄介电壁上,这对p/n 掩模对准提出了挑战。

此外,实际应用中 90% 的器件都具有用于 n 和 p 沟道的公共栅极。在具有内壁forksheet 器件的标准单元中,介电壁会阻碍这种pn 连接栅极。除非将栅极做得更高以跨越该壁,但这又会增加寄生电容。

最后,芯片制造商担心三栅极架构,因为栅极仅从三面包围沟道。与 GAA 结构相比,栅极存在失去对沟道控制的风险,尤其是在沟道长度较短的情况下。

03

“外壁”叉片:CELL边界处的介电壁

在2025年超大规模集成电路技术与电路研讨会(VLSI 2025)上,imec的研究人员展示了一种新颖的forksheet器件架构,并将其命名为“外壁”(outer wall)forksheet。他们通过TCAD仿真展示了这种外壁forksheet如何通过降低工艺复杂性、提供卓 越性能并保持面积可扩展性,从而改进其先前的设计。

图 3 – Imec 的逻辑技术路线图,展示了纳米片时代从 2nm 延伸到 A10 节点,采用外壁forksheet,然后过渡到 A7 及更高版本的 CFET

外壁forksheet将介电壁置于标准单元边界处,使其成为pp或nn wall。这使得每个wall可以与相邻的标准单元共享,并且可以加厚(至约15纳米),而不会影响90纳米的单元高度。

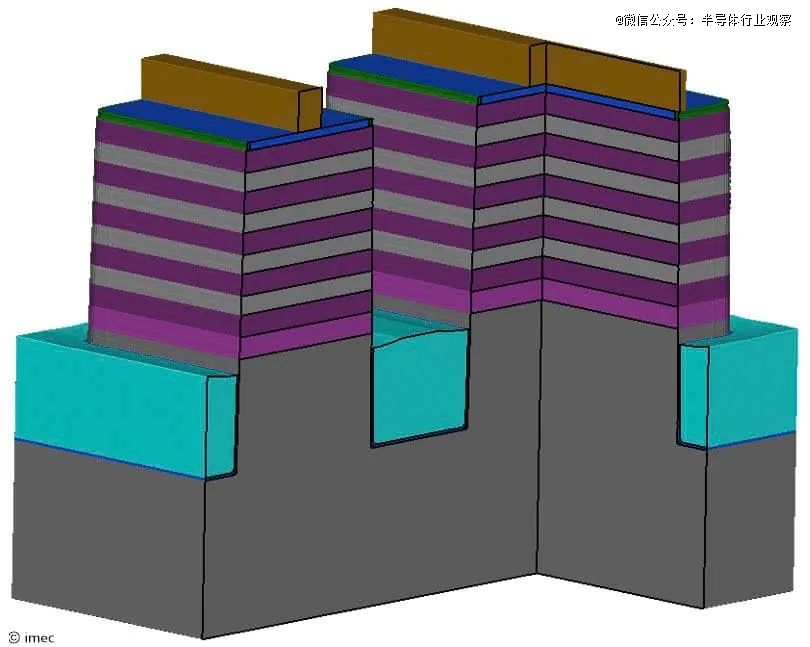

另一个显著特点是wall-last集成方法。整个工艺流程始于形成宽大的Si/SiGe堆叠——这是任何GAA技术中都会重复出现的步骤。在纳米片沟道释放步骤中蚀刻掉SiGe之后,该堆叠的Si层将形成纳米片状的导电沟道。介电壁最终会将该堆叠一分为二,两个极性相似的FET位于壁的两侧。介电壁本身在集成流程接近尾声时进行处理,即在纳米片沟道释放、源极/漏极回蚀和源极/漏极外延生长之后。替换金属栅极 (RMG) 步骤完成了集成流程。

图 4 – (顶部) 内壁和 (底部) 外壁forksheet结构示意图

04

外壁forksheet的 5 项关键改进

与 GAA 纳米片器件相比,内外壁forksheets具有两个共同优势。在面积缩放方面,它们均能够在 A10 节点实现 90nm 逻辑标准单元高度,这与 A14 纳米片技术中 115nm 的单元高度相比更具优势。

第二个共同优势是寄生电容减小:位于壁两侧的两个场效应晶体管 (FET)(内壁为 n 和 p,外壁为 n 和 n/或 p 和 p)可以比基于纳米片的单元放置得更近,而不会引起电容问题。

此外,外壁forksheets有望在五个关键方面超内壁forksheets设计。

首先,由于采用了wall-last集成方法,电介质壁省去了几个复杂的FEOL步骤。因此,它可以由主流的二氧化硅制成。在后壁工艺步骤中,通过在宽Si/SiGe堆叠中形成沟槽并用SiO 2电介质填充来形成壁。

其次,由于wall位于单元边界,其宽度可以放宽至约 15nm,从而简化工艺。

第三,现在可以轻松连接一个标准单元内的n 和 p 器件的栅极,而无需穿过介电壁。

第四,外壁forksheets有望提供优于内壁器件的栅极控制,这与形成Ω-gate而非三栅极forksheets结构的能力相关。更宽的介电壁使得在最后的RMG步骤中对壁进行几纳米的刻蚀成为可能。这使得栅极能够部分环绕沟道的第四个边缘,从而形成W形栅极,增强了对沟道的控制。

通过TCAD模拟,imec的研究人员发现,刻蚀掉5纳米的介电壁是最 佳选择,可将驱动电流提高约25%。

图 5 – 壁面蚀刻对栅极形成的影响:从三栅极到 Ω 栅极,再到 GAA

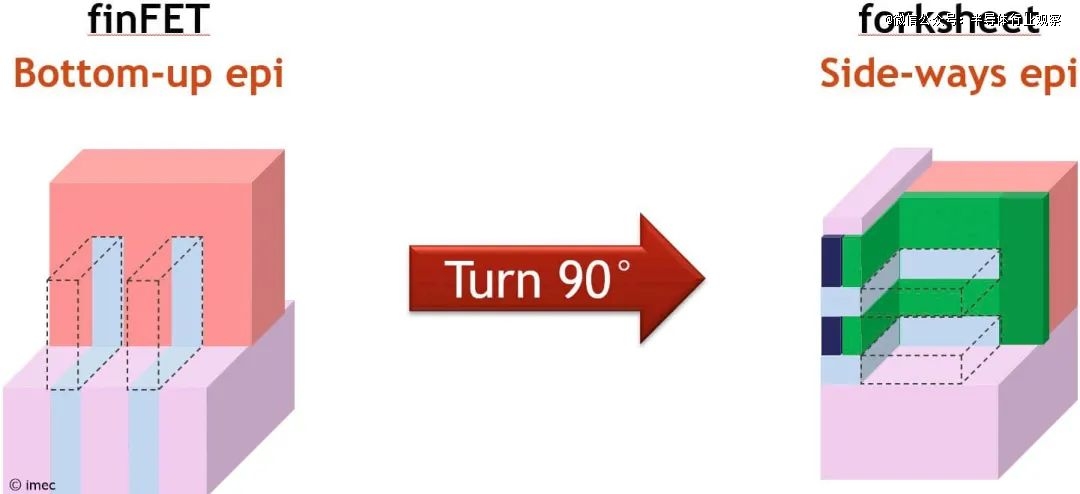

第五个方面与forksheet集成流提供全沟道应变(full channel strain)的潜力相关,这是一种额外的性能提升,有利于驱动电流。通常,可以通过实施源极/漏极应力源来获得全沟道应变。该方法已被证明在(p型)FinFET中非常有效,但在GAA纳米片和内壁 forksheet 器件架构中难以实现。从概念上讲,其思路是将Ge原子并入源极/漏极区域。由于Ge原子比Si原子更大,它们会在Si沟道中引入压缩应变,从而提高载流子的迁移率。

图 6 – 在外壁forksheet 工艺流程开始时,在宽大的 Si(灰色)/SiGe(紫色)层堆栈顶部沉积一层“pre-wall”硬掩模(棕色)。这样,硬掩模下方的 Si“种子晶体”便可支持源极/漏极外延生长

外壁 forksheet 器件之所以能够实现完全有效的源极/漏极应力源,是因为采用了wall-last方法。在制作壁之前,硬掩模会继续覆盖宽 Si/SiGe 堆栈的中间部分,该部分稍后将用于形成壁(图 6)。此硬掩模下方的“Si spine”现在可以在源极/漏极外延生长期间充当种子晶体,充当从一个栅极沟道延续到下一个栅极沟道的硅“template”。这类似于 FinFET 技术中的Si subfin:想象一下将源极/漏极外延模块旋转 90°(图 7)。如果没有这样的硅晶体模板(template),源极/漏极外延界面处就会形成垂直缺陷,从而消除硅沟道内形成的压缩应变。

图 7 – 外壁forksheet中的Si spine(右)提供了从一个栅极沟道到下一个栅极沟道的连续硅晶体模板。这在概念上类似于 FinFET 技术中的Si subfin(左)

05

SRAM 和环形振荡器设计中的

外壁forksheet

最后,imec 进行了一项基准研究,以量化外壁forksheet的功率性能面积 (PPA) 优势。

当比较 A10 外壁forksheet和基于 A14 纳米片的 SRAM 位单元的面积时,纳米片架构的面积优势就变得显而易见。布局显示,基于外壁forksheet的 SRAM 单元面积减少了 22% ,这是由于在栅极间距缩小的基础上,pp 和 nn 间距也减小了。

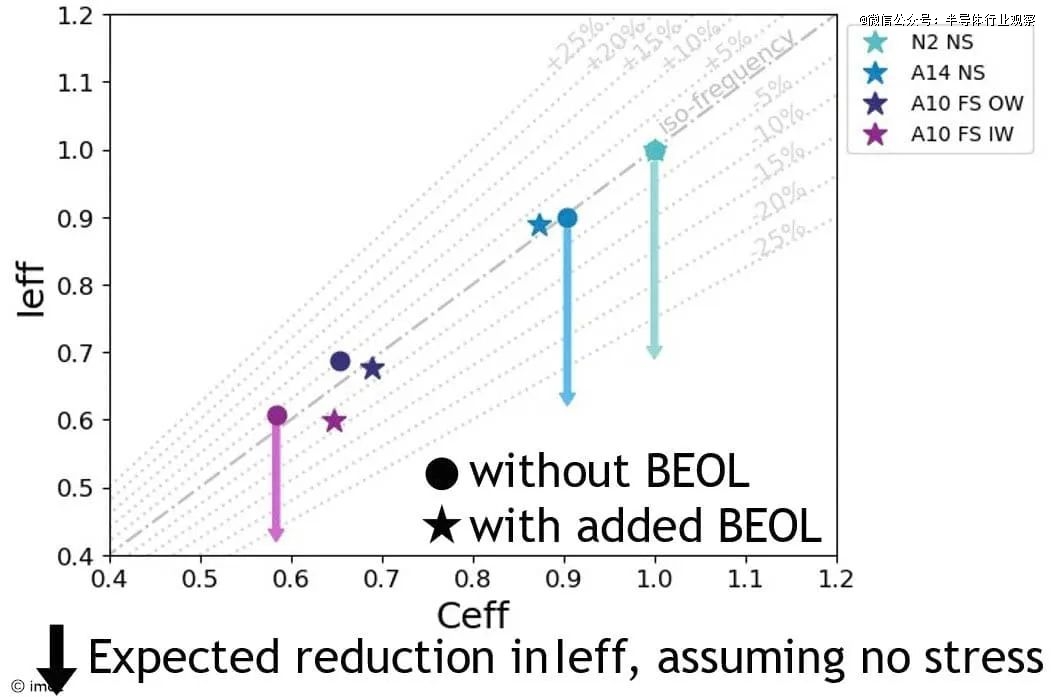

性能评估的另一个关键指标是环形振荡器的模拟频率,表示为有效驱动电流与有效电容之比 (I eff /C eff )。模拟表明,对于 A10 节点,需要一个外壁forksheet来保持与之前的 A14 和 2nm 节点的频率指标一致,前提是所有这些器件结构都能实现全沟道应力。

事实证明,在纳米片(2nm 和 A14)和内壁forksheet器件中实现全沟道应力具有挑战性,它的缺失会导致驱动电流损失约 33%。因此,预计在外壁forksheet器件中实现有效源/漏应力器的能力将在环形振荡器设计中产生进一步的性能优势。

图 8 – 环形振荡器仿真结果(有和没有后端 (BEOL) 负载)

展望与结论

叉片 (forksheet ) 器件架构由 imec 引入,旨在将基于纳米片的逻辑技术路线图扩展到A10 技术节点,并预期 CFET 能够实现量产。由于可制造性问题,imec 放弃了原有的内壁forksheet设计,并开发了“升级”版本:外壁forksheet。与内壁forksheet相比,新设计在提升性能和保持面积缩小的同时,确保了更高的可制造性。

展望未来,imec 目前正在研究外壁forksheet设计与 CFET 架构的兼容性,以及 CFET 能在多大程度上从这种创新的扩展助推器中获得 PPA 效益。

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。