晶圆键合是近十几年快速发展起来的新兴半导体加工技术,在MEMS,CIS和存储芯片等领域有着重要的应用,得到越来越多的关注。

在信息的海洋中,晶圆键合的存在感相比光刻技术显得异常稀薄,但是当我们拿出一台手机,他的图像传感器,重力加速传感器,麦克风,4G和5G射频前端,以及部分NAND,都或多或少应用到了晶圆键合的技术。可以说,晶圆键合技术为我们的信息化生活做出了重要的贡献。

01 键合=接合

晶圆键合(wafer bonding),从名字上就可以同传统封装中应用到的引线键合wire bonding和贴片键合die bonding所区分。日语中,bonding被翻译为接合,从直观印象上更方便于理解这一工艺和过程。

从键合方式上来分类,晶圆键合可以分为*键合和临时键合。区别也顾名思义,*键合后无需再解键合(debonding),而临时键合还需要解键合,将接合在一起的晶圆重新打开。

从界面材料来讲,分为带中间层的胶键合,共晶键合,金属热压键,无中间层的熔融键合(fusion bonding)和阳极键合等。

键合的目的也各不相同,比如为器件提供气密保护,在MEMS和SAW中一定的应用场景;又例如为减薄晶圆提供机械支撑或是层转移,比如IGBT和BSI中的应用就是基于该目的;目前最新也最重要的应用还是晶体管的三维互联,HBM,3D NAND以及正在研发中的互补型场效应晶体管CFET和背部供电网络BPN等,近年来兴起的混合键合(hybrid bonding)便是着眼于这项应用的工艺,该工艺因为同时包含了熔融键合和金属键合的特点而得名。

早期的晶圆键合对于套刻精度的控制要求并不高,键合后在10微米以内即可。但是自BSI开始后的套刻精度要求就到达了1.5微米的水平,而对于3D NAND和高端BSI的应用,更是达到了300纳米以下甚至150纳米的要求!随着键合技术的发展和向前道工艺的渗透,笔者大胆推测,未来可能会达到数十纳米套刻精度的要求。

02 旧酒新瓶装

如先前所述,键合的本质是接合,其利用各种不同的物理和化学方式接合两种界面的原理,早在人类切出*片晶圆前就已经被发现和应用了。无论是借助高分子化合物的胶键合,还是利用焊接原理的共晶键合,甚至是通过超光滑表面之间的范德华力相互吸引的熔融键合,其基本原理在晶圆键合诞生前就早已为人所知了。但晶圆键合真正的大规模工业应用,则是从最近十几年才开始。

1969年,Wallis和Pomerantz*次描述了在500℃下使用电场将硅经验和苏打玻璃晶圆键合在一起,即我们今天所知道的阳极键合。

1986年,IBM和东芝在研究中发现了熔融键合,当硅晶圆被镜面抛光后,即使在室温下不借助其他粘合介质也可通过范德华力互相吸引发生键合,这也是硅-硅直接键合的开端。之后的数年里,用于SOI,MEMS以及III-V族化合物的熔融键合技术被相继发表。90年代后,使用等离子处理晶圆表面的常温键合+低温退火和高真空下的无需退火的熔融键合技术也相继被开发出来。

2016年,索尼首次利用铜-二氧化硅混合键合生产图像传感器。这一始于80年代中期的构想,在经历了十数年的研究后终于成为了现实,为产业界所接受。

通过晶圆键合的方式实现的三维互联的方式有许多,但如同上图中(a)所式的熔融键合方案和(d)所示的混合键合方案,更适合先进的CMOS工艺。

金属热压键合(c)需要使用极高的压力(10-100kN),甚至类似阳极键合还会使用高压电场,对于CMOS的工艺兼容性其实不是那么得友好,容易破坏其前道的金属图形,因此仅需要常温键合+低温退火的熔融键合和混合键合(d)便因其与CMOS良好的工艺兼容性,得到了越来越多的青睐。

熔融键合也并非生来就如此温和,从早期需要1000℃高温进行数小时退火的工艺条件,发展到只需要常压等离子表面活化后常温键合之后,在不足400℃的条件下退火,甚至在超高真空下使用等离子表面活化后无需退火,为其强大的CMOS工艺兼容性提供了保障。而不借助TSV直接使用铜触点进行互联的混合键合,将上下晶圆间的互联距离缩小到了最短,进一步提升了电学性能。

正是因为得益于熔融键合和混合键合的快速发展,扫除了晶圆键合走向CMOS互联工艺的*障碍。

03 熔融键合:从SOI到BSI

熔融键合通常是以硅-硅或硅-二氧化硅为键合界面,经过适当的表面处理后进行接合的工艺。笔者看到过一种说法,只要表面足够光滑和平整,则万物皆可bond,因此磷化铟和铌酸锂这样特殊的衬底也可以同硅晶圆进行熔融键合!

熔融键合早期相对为人所知的应用是用于SOI绝缘体上硅的生产。作为一种光学和电学性能丰富的衬底材料,SOI的制备自然也是比常规的硅片复杂的。裸硅片和热氧片在熔融键合后通过背面减薄的方式,是早期的SOI片的主要制备方式,但是受制于其成本高,生产速度慢,均一性不佳,使得其应用场景相对受限。之后,法国的Soitec开发的SmartCut®技术使得成本,生产速度和均一性指标得到了飞跃性提升,裸硅片作为供体晶圆在熔融键合后,通过氢离子注入后自动断裂,分离供体晶圆,在表面抛光后可重复使用。

熔融键合更为人熟知的应用,则是用于BSI背照式图像传感器的生产。初期的BSI通过作为机械支撑的无图形晶圆与CMOS晶圆熔融键合后,将CMOS背面减薄进行pixel阵列的制作。随着对图像信号处理的需求的发展,将图像处理的逻辑晶圆同CMOS晶圆进行面对面的熔融键合,并以TSV进行互联来实现成为了新的制作方式。当混合键合的技术成熟后,BSI也进入了高密度互联的时代,这便是后话。

除此之外,笔者在一些论文中也见到过使用熔融键合,将micro LED以及MEMS之类的芯片与CMOS进行互联的案例。包括IMEC的CFET技术路线中,也有使用熔融键合来制作三维晶体管的应用,随着半导体三维时代的到来,熔融键合的潜力不可估量。

04 混合键合:新时代名片

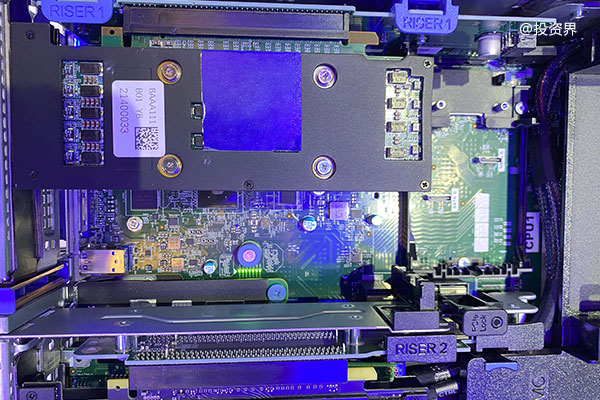

说到混合键合最典型的应用,毫无疑问就是长江存储的Xtacking®了。通过不同的工艺,先后制作Memory晶圆和CMOS晶圆,在后道制程中构建两者的触点。通过混合键合,这些触点被链接导通,Memory和CMOS就在垂直方向实现了互联。

按照Frauebhofer研究所的说法,混合键合的优势有三:

更短的互联距离:不仅不需要用引线互相联通,也无需用TSV穿过整个CMOS层,仅仅通过连接后道的铜触点就可以实现互联

更高的互联密度:铜触点的面积非常小,相比直径百微米的锡球和TSV,混合键合工艺中的铜触点的pitch size甚至都不足10微米,无疑可以实现更高的互联密度

更低的成本:毫无疑问,针对每颗DIE单独进行互联需要更多的时间,通过晶圆键合可以实现大面积高密度的互联,对产能的提升的贡献是飞跃性的!自然,生产成本也可以得以降低

除了先前提到的BSI,诸如micro LED和CMOS进行混合键合的案例也是存在的。最新的研究中,甚至有将micro LED在小尺寸晶圆上制作完成后,分切成独立的DIE重新粘接到一张12寸晶圆上与CMOS 12寸晶圆进行混合键合互联的做法,可见其工艺兼容性是非常优秀的。这也是混合键合的另一大优势,不同技术节点的CMOS也可以通过铜触点进行互联,工艺选择的灵活性也获得了飞跃性的提升!

当然,混合键合并非*无缺,比如无法从最初阶段就知道失效DIE,只有在完成集成,减薄和划片以及通过测试后才能分辨,因此会使成品DIE的良率受到较大影响。其次,键合界面需要超高的平整度,晶圆的内部应力也需要管控以减小晶圆翘曲,这些都对后道工艺控制提出了苛刻的要求。相比传统封装技术,混合键合所需的ISO3以上的洁净等级相比传统封测厂的ISO5的洁净度要求高了许多,对厂务和环境的管控都提出了很高的要求。

05 *玩家

工艺的实现需要依托材料和设备的支持,虽然是后道工艺,但是这其中的玩家却是少之又少,其中来自德国的苏斯(Karl Suss)和奥地利的EVG(EV Group)独占鳌头,日本的佳能和三菱虽然也有特别门类的键合设备,但无论是市占率还是技术水平都无法与这两位*玩家相提并论。国内目前*系统性介绍晶圆键合的资料是《晶圆键合手册》,苏斯和EVG的设备在其中出镜率相当之高,被反复提及,其知名度和*地位不言而喻。

苏斯和EVG的产品线重合度较高,双方几乎同时涵盖了所有类型的键合工艺,除了键合机外,还包括用于晶圆对准的对准机和双面光刻机,以及检测键合精度的量测机台也都有涉足,但实则各有千秋。在国内键合机市场,相较于EVG,苏斯在高校和研究院所的口碑和市占率更好,但工业应用中EVG则更胜一筹。特别是国内的先进BSI产线,EVG的全自动熔融键合机GeminiFB几乎达到了100%的市场份额!

目前国产的键合机依旧以低端为主,上海S公司研制生产的键合机虽然渗透了胶键合和金属键合的市场,但是尚未进入熔融键合的主阵地。而另一家主攻键合机的国内企业是H公司,同S公司一样,H公司是一家以光刻子系统为人所知的企业,其200nm的对准精度尚无法同EVG上一代产品比肩,但也是本土企业的一大突破!此外,还有数家半导体设备制造公司正在开发新的键合设备,毕竟到去年位为止,CIS行业的增长已经持续了10年,市场空间相当广阔!尽管2022年CIS市场迎来了10年来首次下跌,但是随着安防和智慧城市的需求不断增加,CIS的市场足够庞大,也容得下苏斯和EVG之外的玩家。

06 写在最后

过去十年,推进摩尔定律的脚步逐渐放缓,越开越多的半导体公司寻求先进封装来带动芯片性能的提升,异构集成便是其中一解,而晶圆键合工艺为其提供了高效的实现路径,成为有力的候选工艺!

当2022年英特尔和IMEC公布未来的晶体管发展路线,1nm以后进入CFET时代后,笔者就深信熔融键合和混合键合将会从后道走向前道,和high NA以及hyper NA EUV光刻机一同引领下一个15年的半导体行业发展之路!

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。