有目共睹,SiC功率半导体这几年的发展速度几乎超出了所有人意料。其中,由于SiC MOSFET具有取代现有的硅超级结(SJ)晶体管和IGBT技术的潜力,受到了特别关注。

行业老对手和新玩家纷纷涌入,加倍下注这个新兴市场。

实际上,SiC MOSFET的发展历史相当长远,全球SiC产业龙头Wolfspeed的前身Cree公司的创始人之一John Palmour早在1987年就申请了一项涉及在SiC衬底上生成MOS电容器的结构,这项专利后来被视为促成SiC MOSFET诞生的关键。

不过,由于衬底良率、制造工艺等问题,直到2010年左右SiC MOSFET才正式实现商业化。

彼时,Cree推出了市场上*款SiC MOSFET,采用平面栅结构的CMF20120D(另有说法称,2010年罗姆率先推出了*平面型SiC MOSFET)。到了2015年,罗姆率先实现沟槽栅结构SiC MOSFET的量产,这种结构更能够发挥SiC材料的特性,工艺更复杂。

经过近10年的发展,目前在SiC MOSFET的技术路线上,沟槽型SiC MOSFET正在被认为是更有优势的技术路线和发展方向。

01.平面型 or 沟槽型?

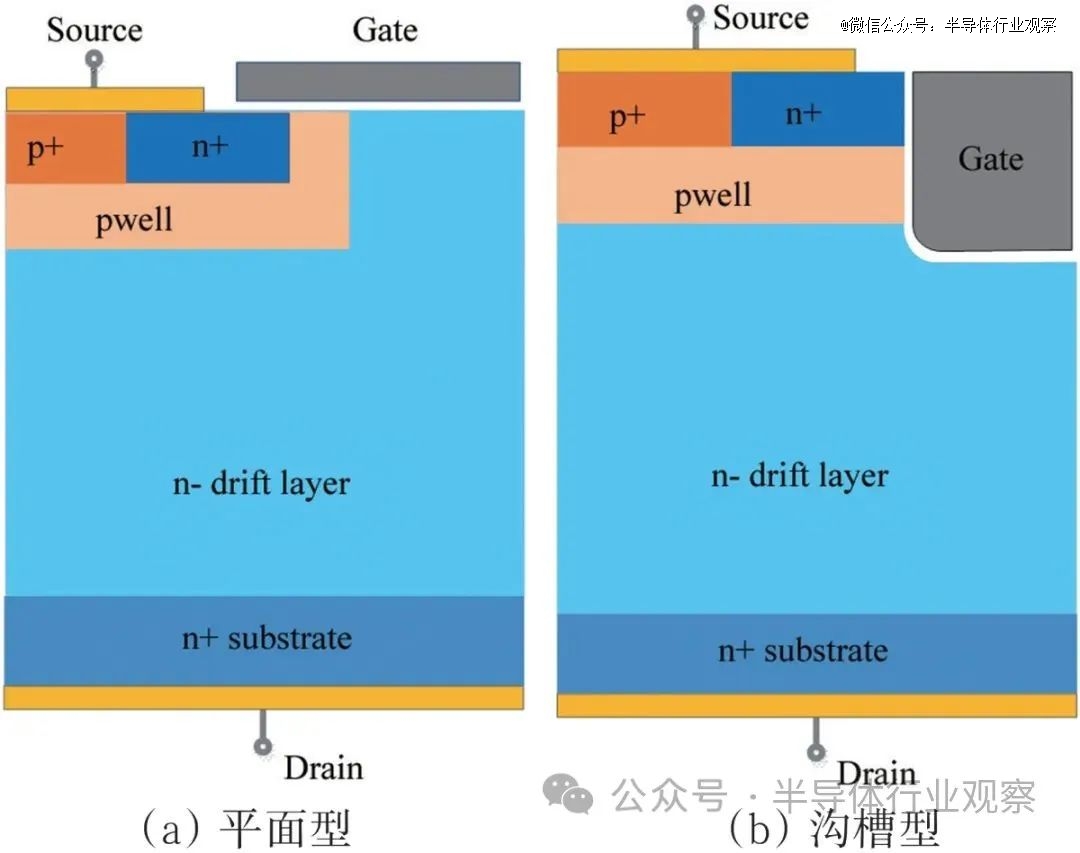

在SiC MOSFET的技术路线之争上,一直有平面栅和沟槽栅两种不同的结构类型。

平面栅和沟槽栅都是垂直导电型的MOSFET,两者在结构上面有相似之处,源极在顶层,漏极在底层,两者的区别在栅极。

平面栅SiC MOSFET结构:是指栅极电极和源极电极在同一水平面上呈现“平面”分布,沟道与衬底平行。平面栅结构的特点是工艺简单,单元的一致性较好,雪崩能量比较高。但是,平面栅SiC MOSFET器件由于JFET区的存在,输入电容较大,从而增加通态电阻,降低了器件的电流能力。

沟槽型SiC MOSFET结构:是指栅极位于源极下方,在半导体材料中形成一个“沟槽”,沟槽栅结构中的沟道和栅极是垂直于衬底的,这也是与平面栅结构的一个显著区别。尽管其工艺复杂,单元一致性比平面结构差。但是,由于沟槽结构没有JFET效应,具有更高的沟道密度,同时沟道所在SiC晶面具有较高的沟道迁移率,因此能够实现更低的比导通电阻,能实现更大电流的导通和更宽的开关速度。

因此,新一代SiC MOSFET主要研究和采用这种结构。

SiC功率MOSFET器件结构

相对而言,平面栅SiC MOSFET工艺复杂度没那么高,而且开发历史比较长,国内外相关产品较早实现量产,并且在特拉斯、比亚迪等众多车企带动下,平面栅SiC MOSFET功率模块自2018年就进入了主驱逆变器。

然而,在缩小芯片尺寸,从而提高产量的过程中,平面栅SiC MOSFET的横向拓扑结构对其最终能够缩小的程度造成了限制。

相比之下,沟槽型SiC MOSFET器件由于采用了沟槽栅极结构,具有以下突出优点:

导电沟道由横向改为纵向,有效节约了器件面积,功率密度大幅提升;

沟槽结构几乎消除了JFET区,使器件输入电容大幅减小,提高了开关速度,降低了开关损耗;

JFET区电阻也随之消除,器件Rdson可以更低电流能力得到进一步提升。

相较平面栅SiC MOSFET器件,沟槽型SiC MOSFET功率密度更大、开关速度更快、导通电阻及损耗更低,因而受到业内企业的高度关注。

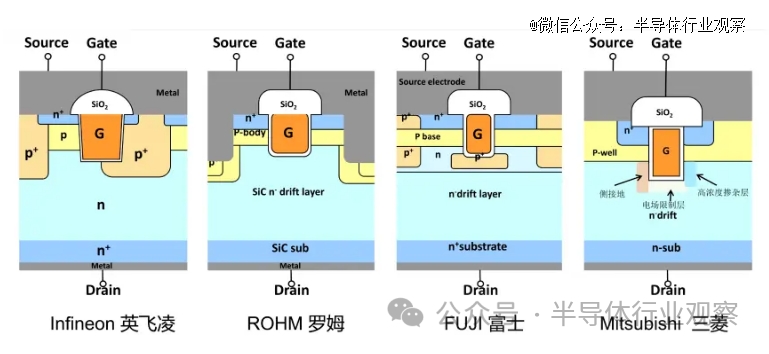

通俗的说,沟槽栅SiC MOSFET可以理解为在平面的基础上“挖坑”,国际SiC厂商们正在通过沟槽栅来更大的发挥SiC的潜力。不过虽说各家都在“挖坑”,但是方式略微有所不同,放眼望去,有的厂商挖一个坑,有的挖两个坑,还有的是斜着挖,各种技术结构层出不穷,百花齐放。

业内几家沟槽栅SiC MOSFET示意图

为此,SiC芯片供应商们尤其是国际大厂都在发挥自家各自的本领,开始了对沟槽型SiC MOSFET的探索。

02.沟槽型SiC MOSFET,多方出击

在一众SiC器件头部供应商中,基本都已经开始向沟槽栅MOSFET进行布局。

罗姆和英飞凌是率先转向沟槽SiC MOSFET的公司。据Yole报告显示,沟槽SiC MOSFET阵营目前从原来的罗姆和英飞凌已经扩大到多家头部大厂,例如住友电工、三菱电机、电装、Qorvo(UnitedSiC)、ST、Wolfspeed、安森美半导体等等,都在从平面结构的MOSFET向沟槽结构转型。

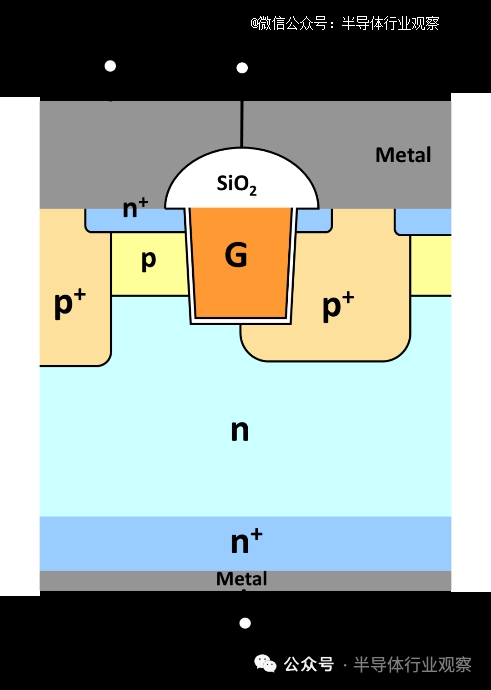

罗姆:双沟槽结构

2015年,罗姆开发并量产了世界*沟槽结构的SiC MOSFET,而且是双沟槽的结构。截止目前,罗姆的沟槽型SiC MOSFET已经发展到了第四代,双沟槽结构同时具有源极沟槽和栅极沟槽。

罗姆双沟槽型SiC MOSFET结构

(图源:罗姆)

在一般的单沟槽结构中,电场集中在栅极沟槽的底部,因此长期可靠性一直是个问题。而罗姆开发的双沟槽结构,在源区也设置了沟槽结构,缓和了栅极沟槽底部的电场集中,这种结构成功地降低了电场,防止了对栅极沟槽处的氧化层破坏,确保了长期可靠性,提高了器件性能。

据了解,在第4代SiC MOSFET中,罗姆进一步改进了双沟槽结构,成功在改善短路耐受时间的前提下,使导通电阻比第三代产品又降低约40%;同时通过大幅降低栅漏电容,成功地使开关损耗比以第三代产品降低约50%。

第4代SiC MOSFET与第3代的导通电阻、开关损耗比较(图源:罗姆)

罗姆预测,第4代SiC MOSFET从2023年起在其销售构成中的占比逐渐增加,直至2024-2025年成为销售主力。

与其他尚在挑战*量产沟槽栅产品的竞争对手相比,罗姆已*数个身位。按照其产品路线图,预计2025年和2028年将推出的第5代和第6代产品的导通电阻将会分别再降低30%。

罗姆的SiC MOSFET技术路线图

英飞凌:半包沟槽结构

众所周知,“挖坑”是英飞凌的*手艺。

在硅基产品时代,英飞凌的沟槽型IGBT和沟槽型的MOSFET就独步天下。随着SiC时代的来临,市面上大部分的SiC MOSFET都是平面型元胞,而英飞凌依然延续了沟槽结构的路线。

英飞凌半包沟槽SiC MOSFET结构示意图

2017年,英飞凌报道了采用半边导通结构的沟槽型SiC MOSFET器件,在栅极沟槽的一边形成导电沟道。从上图看到,参杂毗邻沟槽中的区域是不对称的,沟槽的左侧壁包含了MOS沟道,它被对准到a-plane面,以实现*的沟道迁移率,沟槽底部的大部分被嵌入到沟槽底部下方的p型区域中。

该结构可保护沟槽拐角不受电场峰值影响,提高器件可靠性,同时能进一步提升器件耐压,使得开关控制良好,动态损耗非常低。特别是,该特性对于抑制使用半桥的拓扑中寄生导通引起的额外损耗至关重要。

英飞凌的CoolSiC MOSFET沟槽分立器件系列,采用英飞凌独特的沟槽的方式,为其系统设计带来了许多好处,包括高可靠性、效率提高、实现高开关频率和高功率密度,降低系统复杂性和总系统成本。

英飞凌在2016年推出了*代CoolSiC系列SiC MOSFET,并在2022年更新了第二代产品,相比*代增强了25%-30%的载电流能力。

产能方面,英飞凌目前主要通过特有的“冷切割”技术,减少晶锭切割过程中材料的浪费,未来可以在相同晶锭中获得多一倍的碳化硅衬底来增加产能。另一方面,英飞凌去年宣布投资超过20亿欧元,对位于马来西亚的晶圆厂进行扩建,专门针对碳化硅晶圆进行扩产。

意法半导体:深挖平面潜力,布局沟槽

据Yole数据统计,全球碳化硅功率器件市场份额最高的厂商就是意法半导体(ST),同时凭借与特斯拉的合作,ST的SiC MOSFET产品也是最早在电动汽车上被大规模应用的,自Model3车型开始,特斯拉就一直大规模采用ST供应的碳化硅模块。

在芯片设计上,意法半导体持续深挖平面设计碳化硅MOSFET的技术潜力,2022年推出了第4代平面栅SiC MOSFET。相比上一代产品,第4代平面栅碳化硅的性能有所进步,包括导通电阻减少15%,工作频率增加一倍至1MHz。

而之前规划的沟槽栅产品则顺延成为意法半导体的第5代SiC MOSFET,目前应该在研发阶段,预计2025年量产。

意法半导体SiC MOSFET路线图

(图源:ST)

相比于平面型SiC MOSFET,沟槽型SiC MOSFET可以具有较小的导通电阻,寄生电容较小的同时开关性能更强。

产能方面,ST此前计划在2022财年投入21亿美元来扩大产能,包括扩建原有的6英寸碳化硅晶圆厂、2022投入运营的新加坡6英寸碳化硅晶圆厂。同时,2019年ST收购的瑞典碳化硅衬底生产商Norstel也开始进行8英寸碳化硅材料的测试,预计会在2025年前后可以在新加坡8英寸产线中应用。

安森美半导体:沟槽型产品在即

2021年第3季度,随着收购衬底供应商GTAT的通过,安森美搭建了从碳化硅晶锭、衬底、器件生产到模块封装的垂直整合模式。

虽然其中一些项目的技术实力与各领域*企业还有所差距,但其整体实力却更为均衡:与衬底龙头Wolfspeed相比,安森美的模块封测和量产经验略胜一筹;与器件设计实力超群的英飞凌相比,安森美又有来自GTAT碳化硅材料的加成。

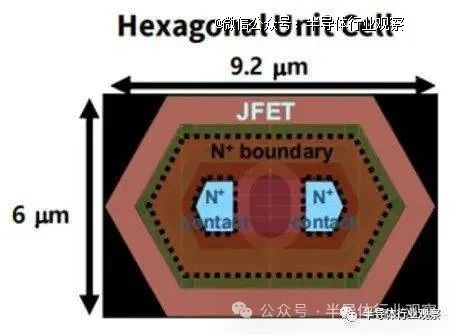

从产品结构来看,安森美的第1代碳化硅MOSFET技术(M1)采用平面设计,耐压等级为1200V。之后从中衍生出900V和750V耐压的规格,微观结构也改为Hex Cell设计,这两个改动相叠加使得碳化硅MOSFET的导通电阻降低了35%左右。目前安森美推出的大部分碳化硅产品均基于M1与其衍生出的M2平台。

目前最新的一代碳化硅技术(M3)仍然采用平面技术,但是改为受专利保护的Strip Cell设计,导通性能较上一代衍生版本再提高了16%。这一代产品将逐渐成为公司的主力车规碳化硅平台,在电压规格上覆盖电动汽车主流的400V和800V平台。

据了解,安森美的下一代技术平台M4则会从平面结构升级为沟槽结构。与初代碳化硅技术相比,沟槽结构的SiC MOSFET在相同载电流的要求下可以减少相当的芯片面积。如果再加上M4平台可能采用8英寸晶圆生产,预期M4的成本较之前将显著降低。

事实上,安森美在沟槽栅方面已经研究了很多年,也有很多样品在进行内部测试,其认为*的问题在于,过早的推出沟槽栅产品在可靠性方面还有一定的风险。所以安森美正在进行可靠性优化,提升沟槽栅的利用率。

同时,在提升可靠性方面,安森美也在对沟槽栅进行摸底,在标准测试的基础上加一些认为有风险的测试点,力图将风险搞清楚。

另外,从封装角度讲,安森美提供各种不同的封装选项,还将推出下一代设计很强的封装,通过封装的不断迭代来适配不同的需求。

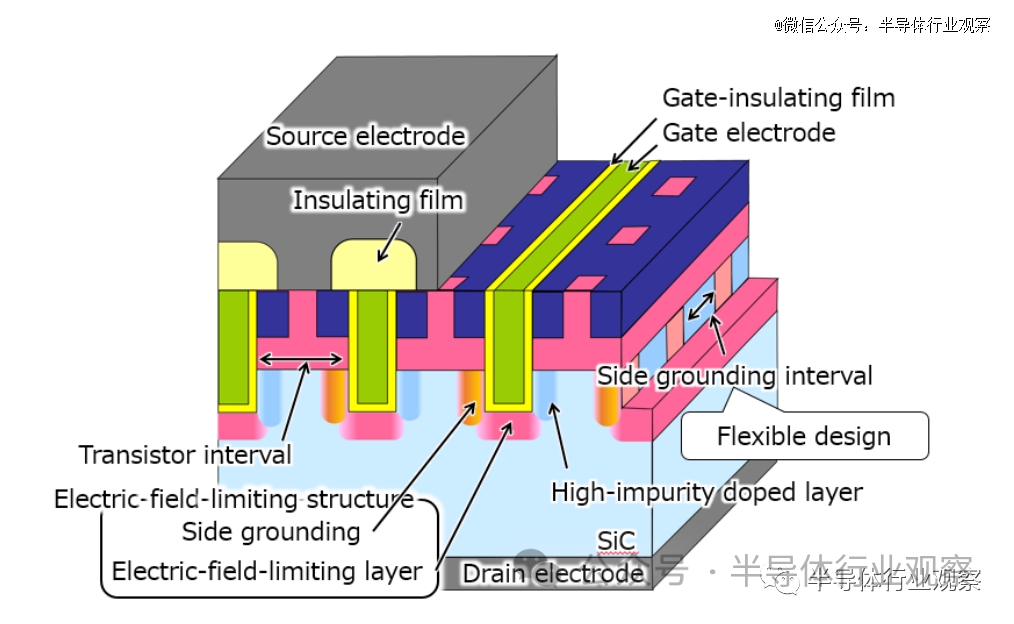

三菱电机:独特电场限制结构

2019年,三菱电机也开发出了一种沟槽的SiC MOSFET,为了解决沟槽型的栅极绝缘膜在高电压下的断裂问题,三菱电机基于在结构设计阶段进行的先进模拟,开发了一种独特的电场限制结构,将应用于栅绝缘薄膜的电场减小到常规平面型水平,使栅绝缘薄膜在高电压下获得更高的可靠性。

三菱电机的新型沟槽型SiC MOSFET结构示意图

(图源:三菱电机)

三菱电机利用独特的电场限制结构确保器件可靠性,通过注入铝和氮来改变半导体层的电气特性,从而保护栅极绝缘膜。

具体来看,在垂直沟槽方向注入铝元素,使沟槽底部形成电场限制层,再通过其新技术斜向注入铝,形成连接电场场限制层和源极的侧接地,并斜向注入氮元素,再局部形成更容易导电的高浓度掺杂层。电场限制层将施加在栅极绝缘膜上的电场降低到传统平面结构水平,保证耐压的同时,提高器件的可靠性。连接电场限制层和源极的侧接地,实现了高速开关动作,减少开关损耗。

与平面结构相比,沟槽型器件Cell pitch更小,所以功率器件能排列更多的元胞。元胞高密度排列使得流动的电流变多,但各栅极的之间的间隔太小就会导致路径变窄,电流流动困难。将氮元素斜向注入,在局部形成更容易导电的高浓度掺杂层,使电流路径上的电流变得容易传输,从而降低电流通路的电阻。与没用高浓度层相比,电阻率降低了约25%。

Wolfspeed:平面栅SiC MOSFET优势未耗尽

作为一家在SiC行业中浸润了超过30年的企业,Wolfspeed及其前身Cree在1991年就推出了*片量产碳化硅衬底。深厚的经验积累和历史沉淀让Wolfspeed的碳化硅衬底性能和质量独占鳌头,就连意法半导体、英飞凌和安森美等同行业竞争对手都不得不花费上亿美元向其采购。因此,Wolfspeed的碳化硅产品获得了至关重要的先发优势,成为了整个碳化硅行业的风向标。

在设计方面,Wolfspeed的碳化硅MOSFET采用平面设计,目前处于第3代,涵盖650V到1200V之间的多个电压规格。与之前两代产品相比,Gen3 平面MOSFET采用六边形晶胞微观设计,导通电阻较上一代Strip Cell减少了16%。

Wolfspeed Gen3 SiC MOSFET采用Hex Cell的平面技术(来源:Wolfspeed)

据了解,Wolfspeed下一代产品将是沟槽栅设计,目前Gen4沟槽栅MOSFET仍在开发中,具体量产时间还没有透露。

尽管也在布局沟槽结构,但从一开始就致力于碳化硅二极管和MOSFET开发的Wolfspeed认为,平面栅SiC MOSFET的技术优势远未耗尽。

Wolfspeed联合创始人John Palmour曾表示:“因为沟槽MOSFET有更好的导通电阻,这是关键性能指标。只要我们在导通电阻方面远远*沟槽SiC MOSFET,我认为没有理由改变这一点,何况我们还将继续改进平面SiC MOSFET。客户不应该关心它是平面MOSFET还是沟槽MOSFET,重要的是特定导通电阻。事实上,我们也不在乎哪种技术路线,我们只关注哪种设计能给客户带来*的利益。”

简而言之,平面结构还有深挖的空间,做好可靠性,也一样有市场。

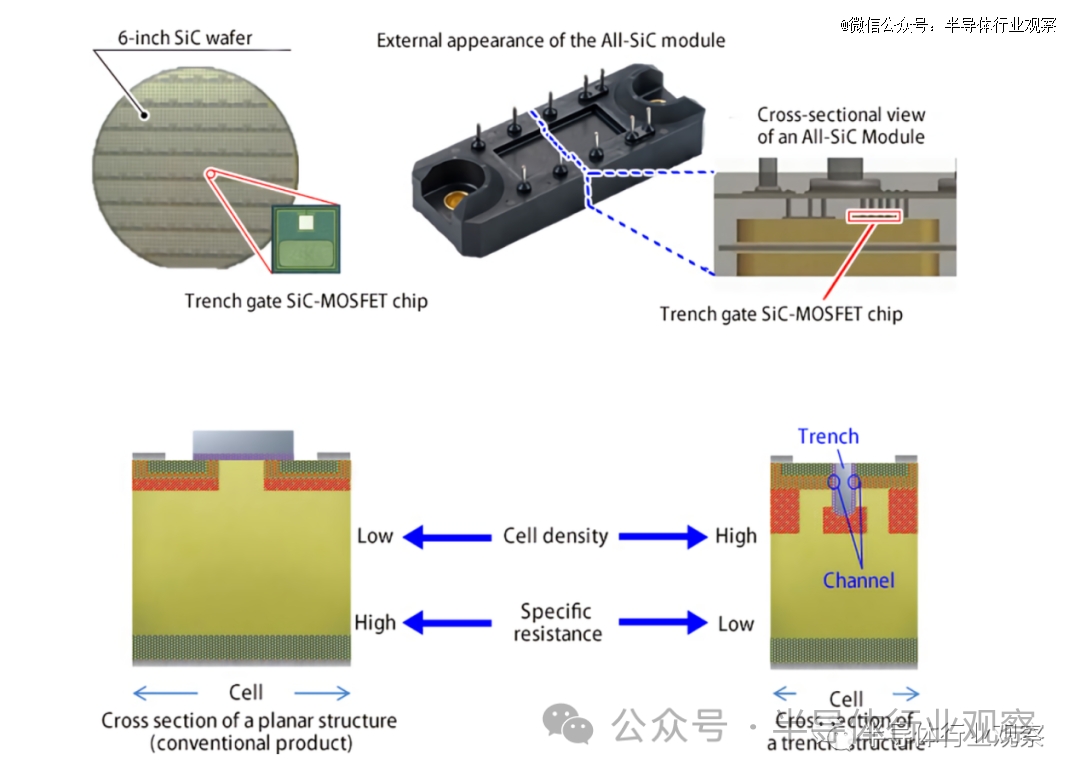

富士电机:全SiC沟槽MOSFET

早在2016年,富士电机就开发了用于全SiC模块的1200V SiC沟槽MOSFET,实现了3.5mΩcm2的低比电阻,阈值电压为5V,同时保持用于打开和关闭电流的“通道”的高可靠性。

由此,与以前的平面结构相比,成功地将电阻率降低了50%以上。此外,富士电机还开发了一种采用独特引脚连接结构的高电流密度专用SiC模块,充分发挥了SiC器件的优点。富士电机已经使用该设备实现了All-SiC模块。

日本住友:V形沟槽

2016年,住友公司研制出具有厚底部氧化层的V型沟槽SiC MOSFET器件样品,进一步提高了器件的栅氧可靠性和阈值稳定性。

住友电工的SiC VMOSFET横截面图

(图源:住友电工)

住友电工利用独特的晶面新开发了V形槽沟槽MOSFET。V-MOSFET具有高效率、高阻断电压、恶劣环境下的高稳定性等优越特性,实现了大电流(单芯片200A),适用于EV和HEV。此外,住友电工正在与国家先进工业科学技术研究所合作开发具有世界*导通电阻的下一代 V-MOSFET。

日本电装:U形沟槽

2023年3月,电装(DENSO)宣布已开发出*采用SiC半导体的逆变器。

其中,电装独特的沟槽型MOS结构采用其专利电场缓和技术的沟槽栅极半导体器件,提高了每个芯片的输出,因为它们减少了由发热引起的功率损耗,独特的结构实现了高电压和低导通电阻操作。

电装的沟槽栅结构(图源:电装)

有资料显示,电装类似于住友的沟槽结构,只是改为了U形沟槽。

图源:松哥电源

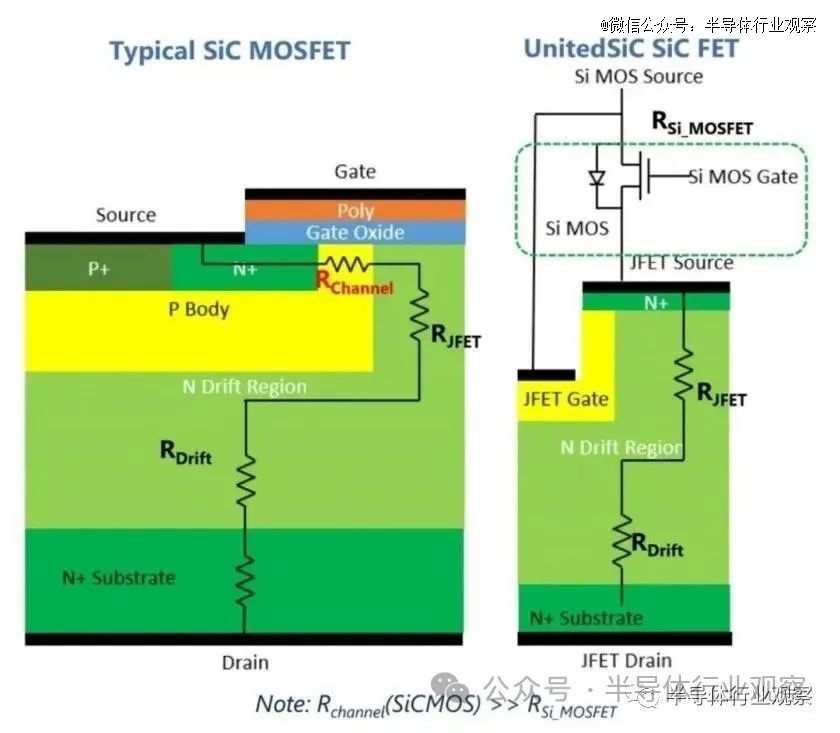

Qorvo:高密度沟槽SiC JFET结构

Qorvo的SiC技术主要来源于2021年收购的UnitedSiC,如今SiC也是Qorvo未来发展的重中之重。

据了解,不同于传统的SiC MOSFET设计,Qorvo另辟新径,其SiC MOSFET采用了高密度沟槽 SiC JFET结构,SiC MOSFET中的沟道电阻Rchannel被SiC FET中低压硅MOSFET的电阻所取代,后者的反转层电子迁移率要好得多,实现了超低单位面积导通电阻,因此损耗也更低。该结构与低电压 Si MOSFET 共同封装,SiC FET的晶粒面积也相对较小。

SiC MOSFET(左)和 Qorvo的SiC FET(右)架构对比(图源:Qorvo)

Qorvo扩充了其1200V产品系列,将其突破性的第四代SiC FET技术推广到电压更高的应用中,产品规格从23mΩ-70mΩ,瞄准800V电动汽车车载充电器(OBC)和直流转换器等应用市场。

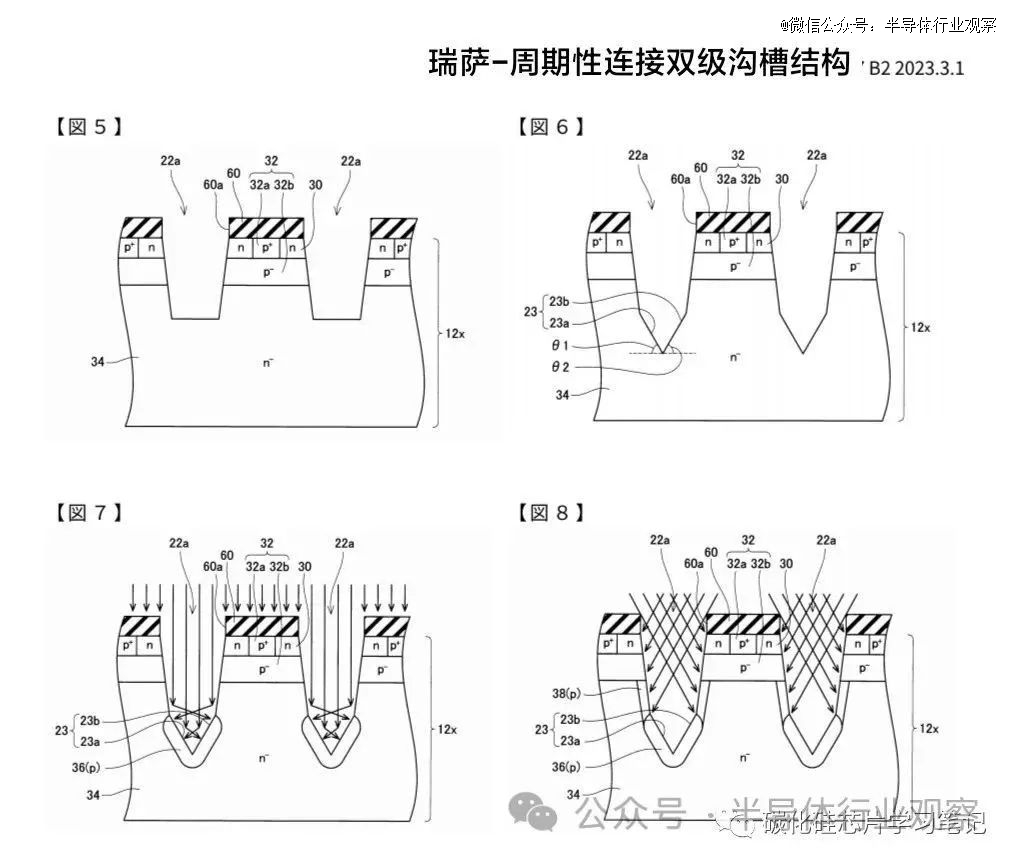

瑞萨电子:变异双级沟槽MOSFET

据了解,瑞萨电子在2023年刚申请了专利,准备研究碳化硅沟槽结构,简称"周期性连接,变异双级沟槽MOSFET”。

图源:碳化硅芯片学习笔记

写在最后

总而言之,提高SiC MOSFET性能的几个重要指标,包括更小的元胞间距、更低的比导通阻、更低的开关损耗、更好的栅氧保护,几乎都指向了沟槽栅结构。

从行业整体来看,目前量产沟槽型SiC MOSFET的主要是欧美日等国际SiC厂商。从国际厂商的布局来看,沟槽栅SiC MOSFET会是未来更具竞争力的方案。

从2015年*款量产沟槽栅SiC MOSFET产品推出到现在过去了近9年时间,众多企业都在开发沟槽栅产品,但目前市面上能够推出量产产品的厂商并不算多。

当然,设计、制造高性能的沟槽栅SiC MOSFET也是国内SiC功率器件发展的当务之急,部分企业已将研究的重心转移至沟槽栅SiC MOSFET。但需要注意的是,国际SiC巨头在SiC MOSFET领域布局多年,积累了不少专利。沟槽结构的高专利壁垒也是国产厂商要迈过去的坎儿。

根据“碳化硅芯片学习笔记”作者的说法:“沟槽SiC MOSFET成套工艺及结构IP,是未来十年碳化硅竞争的入场券!”在目前整体SiC市场持续高速增长的时期,提前布局合适的技术路线,才有机会在未来新的应用市场上占得先机。

参考资料:

[1]2023沟槽大年总结 — 13家碳化硅公司的沟槽MOSFET发展roadmap

[2] 平面型 OR 沟槽型,行业谁具有话语权?碳化硅(SiC)MOSFET的未来发展方向

[3] 西线无战事,碳化硅五巨头的硝烟

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。