在半导体制造中,2nm工艺是继3nm工艺节点之后的下一个MOSFET(金属氧化物半导体场效应晶体管)芯片微缩技术。

“2nm”或“20埃”(英特尔使用的术语)与晶体管的任何实际物理特征(例如栅极长度、金属间距或栅极间距)无关。根据电气和电子工程师协会(IEEE)发布的2021 年更新的《国际设备和系统路线图》中的预测,“2.1 nm节点范围标签”预计接触栅极间距为 45 nm,最紧密金属间距为 20 nm。

一般而言,5nm 芯片每平方毫米的晶体管数量大约在 1.7 亿 - 2 亿个左右。随着制程微缩到 3nm,晶体管密度会有显著提升,能达到每平方毫米 2.5 亿 - 3 亿个左右。而 2nm 制程更是实现了巨大飞跃,其晶体管密度有望超过每平方毫米 3.5 亿个,相较于 3nm 又提升了约 15% - 20%,相比 5nm 提升幅度超 75%。更高的晶体管密度意味着芯片能够同时处理更多的任务,在多线程、并行计算等场景下表现更为出色,无论是运行复杂的科学计算软件,还是处理高清视频流、玩大型 3D 游戏等日常应用,都能带来更流畅的体验。

在功耗方面,芯片制程越小,晶体管在开关状态切换时消耗的电能就越少。到了 2nm 制程,由于晶体管尺寸更小、电阻更低,漏电现象大幅减少,功耗能够比 3nm 芯片再降低 10% - 15% 左右,这对于依靠电池供电的移动设备而言至关重要,可显著延长设备续航时间,如智能手机、平板电脑等,让用户无需频繁充电。

同时2nm 芯片相较于 3nm 芯片,性能有望再提升10% - 20%,能够让计算机启动程序更快、渲染图像更迅速,在人工智能计算、大数据处理等需要快速运算的领域展现更强的实力。

了解完 2nm 芯片在性能与功耗上的优势后,看看全球半导体巨头在该领域的进展。

1. 台积电:一马当先

台积电 2nm(N2)技术开发进展顺利。N2 技术采用该公司*代nm片晶体管技术,在性能和功耗方面实现了全节点跨越,预计今年实现量产。

前不久在旧金山举行的 IEEE 国际电子设备会议 (IEDM) 上,台积电透露了关于2nm的更多细节。

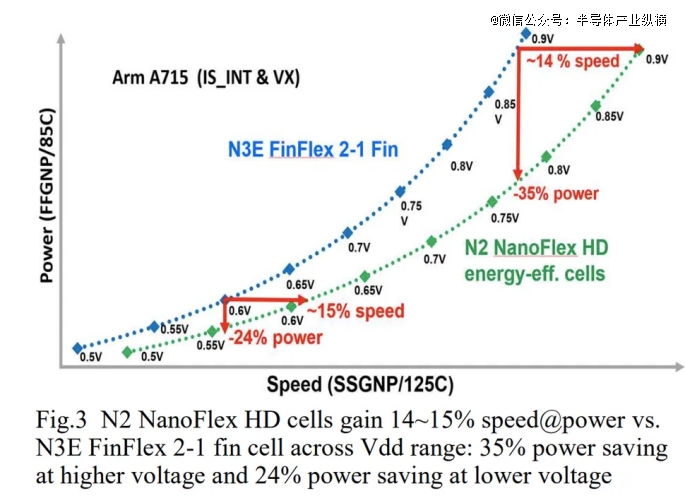

台积电强调,其 2nm 工艺的性能提高了 15%,功耗降低了 30%,显著提高了节点效率。此外,该工艺的晶体管密度提高了 1.15 倍,这归功于全环栅 (GAA) nm片晶体管和 N2 NanoFlex 的使用,这使得制造商能够在最小的面积内塞入不同的逻辑单元,从而优化节点的性能。

通过从传统的 FinFET 技术过渡到专用的 N2“nm片”,台积电成功实现了对电流的更大控制,这使得制造商能够根据工艺用例微调参数。这之所以成为可能,是因为nm片具有一叠狭窄的硅带,每条硅带都被栅极包围;与 FinFET 实现相比,这最终可以实现更精确的控制。

来源:台积电

据称,N2 晶圆每片的价格可能在 2.5-3 万美元之间,具体取决于台积电如何调整,但与 3nm 相比,这是一个巨大的上涨,据说 3nm 的价格约为 2 万美元。更不用说,当你考虑到初始良率和试产时,最终生产会受到更多限制,这意味着该工艺的采用在开始时会比较慢。

此前,据台积电董事长魏哲家称,2nm 晶圆的需求高于上一代 3nm,因此台积电提前试产也是理所当然。台积电已经开始小规模生产先进光刻技术,但目前的产能仅限于 5,000 片晶圆。不过,此前有报道称,该公司在试运行期间已达到 10,000 片,预计今年晚些时候将达到 50,000 片。

到 2026 年,这一数字预计将达到 80,000 片,但尚未确认是同时采用 N2 和 N2P 工艺还是仅采用其中一种。此前,随着宝山和高雄工厂的投入运营,台积电每月的晶圆产量可以达到40,000 片。在进步方面,没有其他代工厂能够与制造商的步伐相匹敌,因此大多数决心推出尖端硅片的公司将寻求台积电的服务也就不足为奇了。

但目前晶圆价格过高也引发了客户的担忧,台积电正在探索降低总成本的新方法,首先是推出名为“CyberShuttle”的服务,该服务将于今年 4 月晚些时候启动。这种方法将允许苹果、高通等公司在同一测试晶圆上评估他们的芯片,从而降低成本。苹果预计将是该代工厂的*个客户,其次是高通和联发科。

但有消息称高通、英伟达等公司因台积电成本高考虑转投三星代工厂。高通在移动芯片领域地位重要,与台积电合作久,很多旗舰芯片由台积电生产,但 2nm 工艺晶圆高价加上台积电可能涨价,使其成本压力大,在智能手机市场芯片成本波动影响产品定价与利润,所以重新审视供应链,三星代工价格低且有 3nm GAA 工艺经验,对高通有吸引力。

英伟达在 GPU 领域*,人工智能发展使其对高性能芯片需求大增,本指望台积电 2nm 工艺提升竞争力,但台积电代工成本高、初始产能有限,阻碍产品推出计划。三星展示 2nm 工艺规划,提出性价比更高方案争取英伟达订单。

台积电清楚自身技术优势难被马上超越,2nm 工艺性能、功耗、晶体管密度优势是吸引客户关键,但也意识到客户流失风险。为应对,除 “CyberShuttle” 服务,还加速内部成本优化流程,加大研发投入提升良率,降低单位成本,同时与客户深度沟通,依客户需求定制芯片代工方案。

目前台积电*的客户苹果已在其工厂预留了 2nm 芯片生产,这让苹果相对于业内其他公司占据了优势。但苹果已推迟使用台积电的 2nm 处理器芯片用于 iPhone 17 Pro 和 iPhone 17 Pro Max,目前商用发布时间定于 2026 年。延迟是因为对台积电 2nm 芯片的高生产成本和有限的制造能力感到担忧。

2. 三星:豪赌未来

三星在 2nm 赛道上同样全力以赴。其计划在 2nm 芯片中集成背面供电网络(BSPDN)技术,将电源线放置在晶圆的背面,这样可以更轻松地在更小的节点尺寸上制造芯片,同时减小芯片尺寸、提高电源效率和性能。据报道,三星铸造厂已经在两个Arm芯片上测试了 BSPDN 技术,使这些芯片的芯片尺寸减小了 10% 和 19%,同时性能和效率提高了最多 9%,测试结果超过了公司的性能目标。

且三星对 2nm 工艺研发投入海量资源,在韩国华城的 “S3” 工厂快马加鞭地安装设备,构建 2nm 生产线,目标指向 2025 年*季度达成每月 7000 片晶圆的产量,并计划在 2025 年末将 “S3” 工厂剩余的 3nm 生产线全面升级为 2nm 生产线,实现产能的迭代升级。

不仅如此,三星还前瞻布局,拟于 2025 年第二季度在韩国平泽的 P2 “S5” 工厂启动 1.4nm 生产线建设,持续向制程工艺极限发起冲击。然而,三星在前行途中并非一帆风顺,3nm 工艺的 Exynos 芯片生产延期、良品率问题如阴霾笼罩,给其带来不小压力。

并且,市场需求的波动也促使三星调整策略,推迟部分工厂的设备采购与建设订单,将部分生产线从晶圆代工转向存储器制造。

由于台积电 2nm 工艺成本高、产能有限,报道称,除了日本 AI 初创公司 Preferred Networks (PFN) 等现有客户外,三星还吸引了国内无晶圆厂公司的兴趣。此外,三星正在与英伟达和高通等大型科技公司合作测试 2nm 工艺,这些公司正在多元化其代工合作伙伴,三星预计将于 2025 年*季度开始试产 2nm 工艺。

这并不是台积电和三星首次争夺高通订单,据悉三星自2020年起已失去高通部分骁龙旗舰芯片订单,其5nm良率也引发担忧。高通计划于 2025 年下半年发布的“骁龙 8 Elite 2”将采用台积电的 N3P 工艺生产。三星曾参与竞标,但最终落败。业内人士称,这可能是三星代工业务的最后机会,目前该业务正面临数十亿美元的损失。

3. 英特尔:紧随其后

曾在芯片制造领域独领风骚的英特尔,虽在先进制程的追逐中一度掉队,却凭借变革决心,强势重返 2nm 战场。英特尔祭出 “四年内五个节点计划”,志在重振芯片制造的昔日辉煌。

在 2nm 技术路线上,英特尔精心规划,旗下的 intel 18A(对标行业 2nm 水准)制程节点预计在 2025 年交付,率先应用于核心产品至强处理器,为数据中心等关键领域注入强劲动力。

英特尔在技术创新方面有诸多举措。其 RibbonFET 晶体管技术是对 Gate All Around 晶体管的创新应用。传统晶体管难以满足高性能需求,RibbonFET 晶体管通过特殊结构设计,加快晶体管开关速度,缩短信号传输延迟,还能在较小空间实现强大驱动电流,兼顾芯片高性能与低功耗,为芯片性能提升开辟新途径。

此外,英特尔推出的 PowerVia 是业界*背面电能传输网络。传统芯片供电、信号线路交织,随着集成度提高,信号干扰严重制约性能提升。PowerVia 技术把电源线置于晶圆背面,分离供电、信号线路,减少信号干扰,提升芯片性能,让芯片在图形渲染、加密解密运算、多任务并行处理等工作中表现更佳。英特尔凭借自身在 CPU 领域的根基与全产业链整合优势,在 2nm 竞争格局中逐步站稳脚跟,向台积电、三星等对手发起挑战,试图改变行业格局。

去年9月,英特尔前任首席执行官帕特·基辛格已将亚马逊的 AWS 作为该公司制造业务的客户,其定制芯片工作将依赖于英特尔的 18A 工艺. 此外,据英特尔临时联席 CEO 米歇尔・约翰斯顿・霍尔索斯在去年12月介绍,英特尔已经为一些客户提供了 Panther Lake 的 E0 工程样品,有 8 个客户已开机,硅晶圆质量很好。在 1月6日的英特尔 CES 2025 演讲中,霍尔索斯还宣布* Intel 18A 制程芯片 —— 英特尔 Panther Lake 处理器将于 今年下半年发布,英特尔会在今年及以后继续增强 AI PC 产品组合,向客户提供*的英特尔 18A 产品样品。

4. Rapidus:奋起直追

在 2024 年 12 月从 ASML 获得*台 EUV 机器后,Rapidus计划于今年4月启用其在日本北海道千岁市兴建的首座2nm以下逻辑芯片工厂“IIM-1”的试产产线,并在2027年开始进行量产。鉴于日本是*获得 ASML 尖端硬件的国家之一,这被认为是日本半导体行业的革命性发展。

去年11 月,日本政府宣布了一项为期七年的计划,在*阶段拨款的约 82 亿美元(1.3 万亿日元)中,有一部分已拨给 Rapidus。截止去年年底,Rapidus 已获得 4645 万美元(73 亿日元)的私人投资和高达 58.55 亿美元(9200 亿日元)的政府援助。然而,预计还需要 254.52 亿美元(4 万亿日元)的额外资金才能在 2027 年启动量产。

且近日有报道称,Rapidus 将与博通合作,力争量产 2 nm尖端芯片,计划 6 月向博通提供试产芯片。消息称博通正评估 Rapidus 的 2 nm芯片良率和性能,如果试产芯片符合其要求,将委托 Rapidus 生产相关高端芯片。

除了博通,Preferred Networks 也委托 Rapidus 代工 2 nm芯片,用于生成式 AI 处理;此外还有消息称 Rapidus 正与 30 至 40 家企业洽谈代工业务,目标是承接定制化的少量多品种半导体订单,与台积电的大规模生产模式形成差异化竞争。

当下,每一家企业的动向都牵动着全球产业链的神经。随着技术的持续演进,成本的优化控制,客户需求的深度挖掘,以及各国政策的扶持引导,2nm 工艺的发展远不止于当下的竞争局面。究竟谁能在这场马拉松式的竞赛中笑到最后?

【本文由投资界合作伙伴微信公众号:半导体产业纵横授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。